# Ferroelectric Field-Effect Transistors Based on MoS<sub>2</sub> and CuInP<sub>2</sub>S<sub>6</sub> Two-Dimensional van der Waals Heterostructure

Mengwei Si,<sup>®</sup> Pai-Ying Liao, Gang Qiu, Yuqin Duan, and Peide D. Ye\*®

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, United States

Supporting Information

ABSTRACT: We demonstrate room-temperature ferroelectric field-effect transistors (Fe-FETs) with MoS<sub>2</sub> and CuInP<sub>2</sub>S<sub>6</sub> two-dimensional (2D) van der Waals heterostructure. The ferroelectric CuInP<sub>2</sub>S<sub>6</sub> is a 2D ferroelectric insulator, integrated on top of MoS2 channel providing a 2D/2D semiconductor/insulator interface without dangling bonds. The MoS<sub>2</sub>and CuInP2S6-based 2D van der Waals heterostructure Fe-FETs exhibit a clear counterclockwise hysteresis loop in transfer characteristics, demonstrating their ferroelectric properties. This stable nonvolatile memory property can also be modulated by the back-gate bias of the MoS<sub>2</sub> transistors because of the tuning of capacitance matching between the MoS<sub>2</sub> channel and the ferroelectric CuInP<sub>2</sub>S<sub>6</sub>, leading to the enhancement of the on/off current ratio. Meanwhile, the CuInP<sub>2</sub>S<sub>6</sub> thin

film also shows resistive switching characteristics with more than four orders of on/off ratio between low- and highresistance states, which is also promising for resistive random-access memory applications.

**KEYWORDS:**  $MoS_2$ ,  $CuInP_2S_6$ , 2D heterostructure, ferroelectric, field-effect transistors, resistive switching

wo-dimensional (2D) semiconductors, such as transition metal dichalcogenides (TMDs), have been extensively explored as channel materials for future electronic device applications because their atomically thin channels offer ideal electrostatic control to enhance the immunity to short channel effects. Molybdenum disulfide (MoS<sub>2</sub>) has been widely studied in recent years as a promising channel material because of its ambient stability, appropriate band gap, and moderate mobility. 1-6 Inserting a ferroelectric insulator (such as hafnium zirconium oxide and lead zirconate titanate) into the gate stack of a metal-oxide-semiconductor field-effect transistor (MOSFET) as a ferroelectric field-effect transistor (Fe-FET) and negative capacitance field-effect transistor (NC-FET) has been widely studied for nonvolatile memory and low-power logic applications. <sup>7-20</sup> The integration of ferroelectric insulators and 2D semiconductor materials as 2D Fe-FETs<sup>7-14</sup> and 2D NC-FETs<sup>15-20</sup> has been proposed and studied to combine the advantages of both 2D semiconductors and ferroelectric-gated FETs. However, the nonideal 3D ferroelectric insulator/2D semiconductor interface leads to interface traps which degrade the device performance, variability, and reliability. The lack of dangling bonds on the surface of 2D materials also makes the atomic layer deposition (ALD) process of ferroelectric insulators difficult.<sup>21</sup> How to integrate an ALD ferroelectric insulator (i.e., hafnium zirconium oxide) as a top-gate dielectric on 2D

materials remains a challenge. The integration of 2D ferroelectric insulators together with 2D semiconductors as 2D van der Waals (vdW) heterostructures can be a potential solution to eliminate the interface issue, reduce the interface trap density, and achieve high-performance Fe-FETs. However, 2D ferroelectric material is rather rare because ferroelectricity tends to disappear on very thin films and requires breaking of the structural centrosymmetry. <sup>22,23</sup> A few 2D materials have been studied theoretically <sup>23–26</sup> and experimentally <sup>27–30</sup> that show ferroelectricity. The choice of a proper 2D ferroelectric insulator to integrate with 2D semiconductors is crucial because 2D vdW heterostructure Fe-FETs require a low leakage current gate insulator and room-temperature ferroelectricity for real device applications. Among these materials, CuInP<sub>2</sub>S<sub>6</sub> (CIPS) has been recently explored as a roomtemperature 2D ferroelectric material with switchable polarization down to ~4 nm and low leakage current, which can be a promising candidate for 2D vdW heterostructure Fe-FETs.<sup>29-32</sup>

In this work, we synthesize the bulk CIPS crystal and examine the ferroelectricity of the 2D CIPS thin film by

Received: March 9, 2018 Accepted: June 26, 2018 Published: June 26, 2018

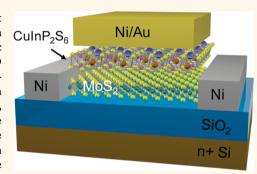

Figure 1. (a) Schematic view of a  $MoS_2/CIPS$  2D heterostructure Fe-FET. Few-layer  $MoS_2$  is applied as the channel material. Fifteen nanometer Ni is used as the source/drain electrodes. The back-gate stack includes heavily n-doped Si as the gate electrode and 300 nm  $SiO_2$  as the gate dielectric. The top-gate stack consists of CIPS as the ferroelectric gate insulator and Ni/Au as the gate electrode. (b) Top-view false-color SEM image of fabricated  $MoS_2/CIPS$  2D heterostructure Fe-FETs with different channel lengths, capturing Ni/Au top-gate electrodes, Ni source/drain electrodes, CIPS ferroelectric gate insulators, and  $MoS_2$  channels.

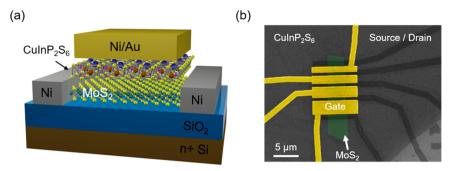

Figure 2. Fabrication process of  $MoS_2/CIPS$  2D heterostructure Fe-FETs. (a)  $MoS_2$  FET fabrication. (b)  $CuInP_2S_6$  growth and exfoliation. (c)  $CuInP_2S_6$  dry transfer. (d) Gate metal deposition.

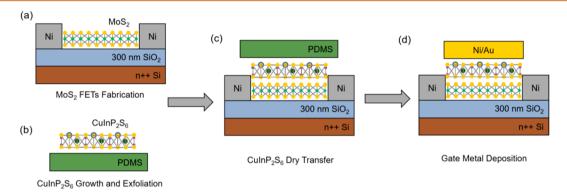

Figure 3. (a) Raman spectrum of exfoliated CIPS thin film at room temperature. (b) EDS spectrum of exfoliated CIPS thin film. The atomic percent (atom %) of S, P, Cu, and In is 59.9, 20.3, 10.3, and 9.6, respectively. EDS analysis shows almost perfect CuInP<sub>2</sub>S<sub>6</sub> stoichiometry. (c) Polarization—voltage measurement at 290 K on ferroelectric CIPS MIM capacitor (Ni/0.6  $\mu$ m CIPS/Ni). (d) Temperature dependence of remnant polarization on the CIPS thin film measured using the same capacitor as in (c), suggesting a ferroelectric Curie point at ~315 K.

electrical polarization–voltage (P-V) measurement. We demonstrate  $MoS_2/CIPS$  2D vdW heterostructure Fe-FETs at room temperature. The ferroelectric CIPS is integrated on

top of the  $MoS_2$  channel as a ferroelectric insulator, which offers a 2D/2D semiconductor/insulator interface. The  $MoS_2/CIPS\ 2D\ vdW$  heterostructure Fe-FETs exhibit a clear

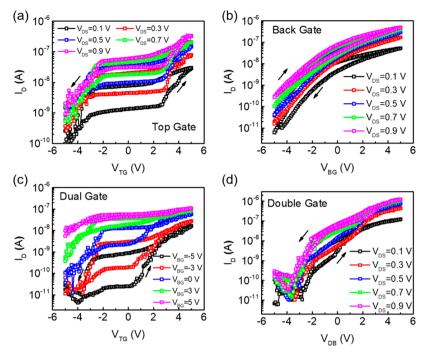

Figure 4. (a) Top-gate  $I_{\rm D}-V_{\rm GS}$  characteristics of a MoS<sub>2</sub>/CIPS 2D heterostructure Fe-FET measured at room temperature with a floating back-gate. The device has a channel length of 1  $\mu$ m and channel width of 2.1  $\mu$ m. The thickness of the MoS<sub>2</sub> flake is about 7 nm, and the thickness of the CIPS thin film is about 0.4  $\mu$ m. (a) Back-gate  $I_{\rm D}-V_{\rm GS}$  characteristics measured at room temperature with a floating top-gate, using the same MoS<sub>2</sub>/CIPS 2D heterostructure Fe-FET as in (a). (c) Top-gate  $I_{\rm D}-V_{\rm GS}$  characteristics at  $V_{\rm DS}=0.1$  V and at various  $V_{\rm BG}$  measured at room temperature, using the same MoS<sub>2</sub>/CIPS 2D heterostructure Fe-FET as in (a). (d)  $I_{\rm D}-V_{\rm GS}$  characteristics with the same  $V_{\rm TG}$  and  $V_{\rm BG}$  measured at room temperature, using the same MoS<sub>2</sub>/CIPS 2D heterostructure Fe-FET as in (a).

counterclockwise hysteresis loop in transfer characteristics, demonstrating their ferroelectric properties. Meanwhile, this stable nonvolatile memory property can also be modulated by the back-gate bias of the MoS<sub>2</sub> transistors because of the tuning of capacitance matching between the MoS<sub>2</sub> channel and the ferroelectric CuInP<sub>2</sub>S<sub>6</sub>, which leads to the enhancement of the on/off current ratio. Meanwhile, the resistive switching characteristics of CIPS are also studied, and more than four orders of on/off ratio between low- and high-resistance states are realized.

## **RESULTS AND DISCUSSION**

The schematic view of a MoS<sub>2</sub>/CIPS 2D heterostructure Fe-FET is shown in Figure 1a. The device consists of few-layer MoS<sub>2</sub> as the channel material, a few hundred nanometer CIPS as the ferroelectric gate insulator for a top-gate Fe-FET, a 300 nm SiO<sub>2</sub> as the back-gate insulator, and heavily doped silicon substrate as the back-gate electrode. The 40 nm Ni/50 nm Au is used as top-gate electrode, and 15 nm Ni is used as source/ drain electrodes. The device has a dual-gate structure, in which the MoS<sub>2</sub> channel can be controlled by both top-gate and backgate. A top-view false-color scanning electron microscopy (SEM) image of several fabricated devices with different channel lengths  $(L_{ch})$  is shown in Figure 1b, capturing Ni/Au top-gate electrodes, Ni source/drain electrodes, CIPS ferroelectric gate insulators, and MoS2 channels. The detailed fabrication process is shown in Figure 2, and detailed information can be found in the Methods section.

Figure 3a illustrates the Raman spectrum of an exfoliated CIPS thin film at room temperature, showing the same characteristics as those reported in bulk CIPS crystals at ferroelectric phase.  $^{33}$  Cation (Cu<sup>I</sup>, In<sup>III</sup>) and anion ( $P_2S_6^{4-}$ )

vibrations are responsible for peaks in the 50-80, 90-140, and 300-320 cm<sup>-1</sup> ranges. Multiple peaks between 140 and 290 cm<sup>-1</sup> are caused by S-P-P and S-P-S modes, and the peak at 380 cm<sup>-1</sup> corresponds to P-P stretching. The 410-460 cm<sup>-1</sup> peaks correspond to P-S oscillations. Figure 3b shows the energy-dispersive spectroscopy (EDS) spectrum of the exfoliated CIPS thin film. The atomic percent (atom %) of S, P, Cu, and In is 59.9, 20.3, 10.3, and 9.6, respectively. EDS analysis shows near perfect CuInP<sub>2</sub>S<sub>6</sub> stoichiometry. The CIPS thin film samples used in Raman and EDS measurement were mechanically exfoliated from a bulk CIPS crystal (the synthesis of the bulk CIPS crystal is discussed in Supporting Information section 1) onto a silicon substrate with 300 nm thermally grown SiO<sub>2</sub>. The atomic structure illustration of CIPS is shown in Supporting Information section 2. It contains an ABC sulfur stacking filled by Cu, In, and a P-P pair. The noncentrosymmetric structure leads to spontaneous polarization and ferroelectricity at temperatures below the Curie point.<sup>31</sup> To study the ferroelectric properties of the CIPS thin film, metal-insulator-metal (MIM, Ni/CIPS/Ni) capacitors are fabricated as a test structure. The P-V characteristics are measured from 290 to 330 K. Figure 3c shows the P-V measurement at 290 K on a CIPS MIM capacitor with a CIPS thickness ( $T_{\rm FE}$ ) of ~0.6  $\mu$ m. The P-V characteristic of CIPS shows a clear ferroelectric hysteresis loop with 3.2  $\mu$ C/cm<sup>2</sup> remnant polarization ( $P_r$ ) and  $8.9 \times 10^{-3} \text{ V/nm}$  coercive field  $(E_c)$ . Note that the success in P-V measurement of the CIPS MIM capacitor suggests that the leakage current through CIPS is sufficiently low, which indicates CIPS can be a good candidate as a ferroelectric gate insulator for Fe-FETs and NC-FETs. Figure 3d shows the temperature-dependent remnant polarization of CIPS extracted from the P-V measurement of the same device as in Figure 3c from 290 to 330 K. The  $P_r$  of

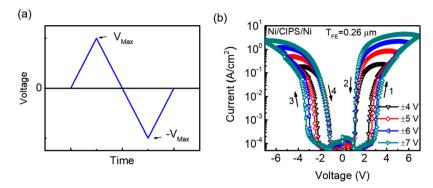

Figure 5. (a) Illustration of I-V measurement on the ferroelectric CIPS MIM capacitors. The voltage across the MIM capacitor was first swept from 0 V to a positive  $V_{\text{Max}}$  and then to a negative  $-V_{\text{Max}}$  and back to 0 V. (b) I-V characteristics at different sweep ranges of a ferroelectric CIPS MIM capacitor with a CIPS thickness of about 0.26  $\mu$ m at room temperature, showing ferroelectric resistive switching with more than four orders of on/off ratio between low- and high-resistance states.

CIPS starts to drop rapidly at about 315 K, suggesting that the Curie point of ferroelectric to paraelectric phase transition is about 315 K. The detailed temperature-dependent P-V measurements can be found in Supporting Information section 4.

Figure 4 shows the electrical characterization of a MoS<sub>2</sub>/ CIPS 2D vdW heterostructure Fe-FET at room temperature. The device has a channel length of 1  $\mu$ m and channel width of 2.1  $\mu$ m. The thickness of the MoS<sub>2</sub> flake ( $T_{\rm ch}$ ) is about 7 nm, and the thickness of CIPS thin film is about 0.4  $\mu$ m. Figure 4a shows the  $I_D$ - $V_{GS}$  characteristics measured using the top-gate (0.4  $\mu$ m CIPS as ferroelectric gate insulator) with the backgate floating at top-gate voltage  $(V_{TG})$  from -5 to 5 V and at drain-to-source voltage  $(V_{\rm DS})$  from 0.1 to 0.9 V. The gate leakage current is smaller than drain current at all different gate voltages, so that the leakage current through CIPS does not have impact on the  $I_D$ – $V_{GS}$  characteristics. The simultaneously measured gate leakage current can be found in Supporting Information section 3. The transfer characteristics show a clear ferroelectric hysteresis loop (counterclockwise) at all  $V_{DS}$ . A larger on/off ratio between the low- and high-resistance state can be observed at lower  $V_{\rm DS}$ . Figure 4b shows the  $I_{\rm D}-V_{\rm GS}$ characteristics measured using the back-gate (300 nm  $SiO_2$  as gate insulator) with the top-gate floating at back-gate voltage  $(V_{\rm BG})$  from -5 to 5 V and at  $V_{\rm DS}$  from 0.1 to 0.9 V. The transfer characteristics show a clockwise hysteresis loop, which is common in MoS2 MOSFETs and is induced by charge trapping at the SiO<sub>2</sub>/MoS<sub>2</sub> interface and in bulk SiO<sub>2</sub>. The characteristics have minor changes of top-gate or bottom-gate being grounded instead of floating, showing the two gates' capacitance coupling has a minor effect on each other. Figure 4c shows the  $I_{\rm D} - V_{\rm GS}$  characteristics measured using the topgate (0.4  $\mu$ m CIPS as gate insulator) at  $V_{\rm DS}$  = 0.1 V with different  $V_{\rm BG}$  from -5 to 5 V. The ferroelectric hysteresis loop in the  $I_D$ – $V_{GS}$  characteristics is found to be modulated by the back-gate bias, as shown in Figure 4c. With more negative  $V_{\rm BG}$ a larger hysteresis loop can be observed, which suggests that back-gate bias can be used to modulate the on/off current ratio of the MoS<sub>2</sub>/CIPS 2D vdW heterostructure Fe-FETs for better memory performance. The origin of the modulation of the ferroelectric hysteresis loop comes from the capacitance matching between the capacitance of CIPS  $(C_{FE})$  and the semiconductor capacitance  $(C_S)$  of the MoS<sub>2</sub> channel. For a ferroelectric-gated FET, it is already known that because of the negative capacitance effect of the ferroelectric material, if  $|C_{FE}|$

<  $C_S$ , the ferroelectric-gated FET is a Fe-FET with hysteresis, whereas if  $|C_{FE}| > C_S$ , the ferroelectric-gated FET is a NC-FET without hysteresis if parasitic capacitance is negligible. A detailed analysis on the value of  $|C_{FE}|$  and  $C_S$  is discussed in Supporting Information section 6. Therefore, as the back-gate voltage can affect the electrostatics in the MoS<sub>2</sub> channel and also tune the  $C_S$ , the back-gate bias can modulate the capacitance matching between  $C_{FE}$  and  $C_S$ , so that the ferroelectric hysteresis loop can be modulated. It also indicates that this dual-gate structure enables the electrically controllable reconfiguration of the devices as either logic devices or memory devices by applying proper back-gate voltage. Figure 4d shows the  $I_D$ - $V_{GS}$  characteristics measured using the same  $V_{TG}$  and  $V_{BG}$  at  $V_{DS}$  from 0.1 to 0.9 V, which is simply the result of impact from both gates.

Except for the ferroelectricity in the CIPS thin film and its applications in Fe-FETs, the CIPS with a MIM capacitor structure also shows resistive switching characteristics which can be used in nonvolatile resistive random-access memory (ReRAM) applications, as shown in the Figure 5. Figure 5a illustrates the I-V measurement process on the MIM capacitors. The voltage across the capacitor was first swept from 0 V to a positive maximum voltage  $(V_{\text{Max}})$  then to a negative  $-V_{\text{Max}}$  and then back to 0 V. Figure 5b shows the I-Vcharacteristics with different gate voltage sweep ranges ( $V_{\rm Max}$ from 4 to 7 V) of a CIPS MIM capacitor with  $T_{\rm FE}$  = 0.26  $\mu$ m, measured at room temperature, showing ferroelectric resistive switching with more than four orders of on/off ratio between low- and high-resistance states. The resistive switching between the low- and high-resistance states originates from the ferroelectric polarization switching, which leads to the change of band alignment between metal and CIPS.<sup>34</sup> The detailed band diagrams in different polarization states are discussed in Supporting Information section 7. The resistive switching characteristics of the CIPS are also affected by  $V_{\rm Max}$ . A larger  $V_{\text{Max}}$  leads to a smaller on-resistance but a larger voltage to reset to high-resistance state, as shown in Figure 5b, which can enable multiple design rooms. These results suggest that CIPS is a promising 2D material for nonvolatile ReRAM applications also.

#### **CONCLUSION**

In summary, MoS<sub>2</sub>/CIPS 2D vdW heterostructure Fe-FETs at room temperature are demonstrated. The ferroelectric CIPS is integrated on top of the MoS<sub>2</sub> channel as a ferroelectric

insulator, which offers a 2D/2D semiconductor/insulator interface. The MoS<sub>2</sub>/CIPS 2D vdW heterostructure Fe-FETs exhibit a stable ferroelectric hysteresis loop in transfer characteristics. Meanwhile, this stable nonvolatile memory property can also be modulated by the back-gate bias of the MoS<sub>2</sub> transistors because of the tuning of capacitance matching between the MoS<sub>2</sub> channel and the ferroelectric CuInP<sub>2</sub>S<sub>6</sub>, leading to the enhancement of the on/off current ratio. Meanwhile, the resistive switching characteristics of CIPS are also studied, with more than four orders of on/off ratio between low- and high-resistance states demonstrated.

#### **METHODS**

**CulnP<sub>2</sub>S<sub>6</sub> Growth.** Single-crystal CIPS were grown by solid-state reaction based on previous works.<sup>32</sup> The detailed growth process can be found in Supporting Information section 1.

**Device Fabrication.** MoS<sub>2</sub> was transferred onto a 300 nm SiO<sub>2</sub>/Si substrate using Scotch tape exfoliation. Fifteen nanometer Ni was deposited by electron-beam evaporation, followed by a lift-off process as a MoS<sub>2</sub> back-gate transistor. The procedure to transfer CIPS on top of MoS<sub>2</sub> is based on a dry transfer process.<sup>35</sup> CIPS was first mechanically exfoliated onto a polydimethylsiloxane (PDMS) substrate. Then the PDMS/CIPS film was stamped on top of the MoS<sub>2</sub> channel. The PDMS film was then removed mechanically because of the stronger adhesion between CIPS and the substrate. Another 40 nm Ni and 50 nm Au were then deposited by electron-beam evaporation and realized by a lift-off process.

**Device Characterization.** The thickness of the CIPS was measured using a Veeco Dimension 3100 atomic force microscope system. SEM and EDS analysis were done using a Hitachi S-4800 FE-SEM and an Oxford X-Max silicon drift detector. Electrical characterization was carried out with a Keysight B1500 system with a Cascade Summit probe station. P-V measurement was done using a Radiant RT66C ferroelectric tester. Raman measurements were carried out on a HORIBA LabRAM HR800 Raman spectrometer.

## **ASSOCIATED CONTENT**

## S Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsnano.8b01810.

Additional details for CIPS growth and structures, gate leakage current, temperature-dependent P-V and I-V measurement, Landau coefficients extraction, and band diagrams of CIPS-resistive switching mechanism (PDF)

### **AUTHOR INFORMATION**

#### **Corresponding Author**

\*E-mail: yep@purdue.edu.

ORCID ®

Mengwei Si: 0000-0003-0397-7741 Peide D. Ye: 0000-0001-8466-9745

## **Author Contributions**

M.S. and P.-Y.L. contributed equally to this work. P.D.Y. conceived the idea and supervised the experiments. P.-Y.L. synthesized the CuInP<sub>2</sub>S<sub>6</sub>. M.S. and P.-Y.L did the device fabrication, electrical measurement, and analysis. G.Q. did the Raman spectrum measurement. Y.D. conducted EDS analysis. M.S., P.-Y.L, and P.D.Y. cowrote the manuscript, and all authors commented on it.

#### **Notes**

The authors declare no competing financial interest.

### **ACKNOWLEDGMENTS**

The authors would like to thank Prof. M. A. Alam for valuable discussions.

#### REFERENCES

- (1) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (2) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 2012, 6, 8563–8569.

- (3) Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS, Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- (4) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-high Vacuum Metal Deposition. *Nano Lett.* **2016**, *16*, 3824–3830.

- (5) Liu, Y.; Guo, J.; Wu, Y.; Zhu, E.; Weiss, N. O.; He, Q.; Wu, H.; Cheng, H.-C.; Xu, Y.; Shakir, I.; Huang, Y.; Duan, X. Pushing the Performance Limit of Sub-100 nm Molybdenum Disulfide Transistors. *Nano Lett.* **2016**, *16*, 6337–6342.

- (6) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H.-S. P.; Javey, A. MoS<sub>2</sub> Transistors with 1-nanometer Gate Lengths. *Science* **2016**, 354, 99–102.

- (7) Lee, H. S.; Min, S.-W.; Park, M. K.; Lee, Y. T.; Jeon, P. J.; Kim, J. H.; Ryu, S.; Im, S. MoS<sub>2</sub> Nanosheets for Top-Gate Nonvolatile Memory Transistor Channel. *Small* **2012**, *8*, 3111–3115.

- (8) Zhang, X.-W.; Xie, D.; Xu, J.-L.; Sun, Y.-L.; Li, X.; Zhang, C.; Dai, R.-X.; Zhao, Y.-F.; Li, X.-M.; Li, X.; Zhu, H.-W. MoS<sub>2</sub> Field-Effect Transistors with Lead Zirconate-Titanate Ferroelectric Gating. *IEEE Electron Device Lett.* **2015**, *36*, 784–786.

- (9) Lipatov, A.; Sharma, P.; Gruverman, A.; Sinitskii, A. Optoelectrical Molybdenum Disulfide (MoS<sub>2</sub>)-Ferroelectric Memories. *ACS Nano* **2015**, *9*, 8089–8098.

- (10) Wang, X.; Wang, P.; Wang, J.; Hu, W.; Zhou, X.; Guo, N.; Huang, H.; Sun, S.; Shen, H.; Lin, T.; Tang, M.; Liao, L.; Jiang, A.; Sun, J.; Meng, X.; Chen, X.; Lu, W.; Chu, J. Ultrasensitive and Broadband MoS<sub>2</sub> Photodetector Driven by Ferroelectrics. *Adv. Mater.* **2015**, *27*, 6575–6581.

- (11) Kobayashi, T.; Hori, N.; Nakajima, T.; Kawae, T. Electrical Characteristics of MoS<sub>2</sub> Field-effect Transistor with Ferroelectric Vinylidene Fluoride-Trifluoroethylene Copolymer Gate Structure. *Appl. Phys. Lett.* **2016**, *108*, 132903.

- (12) Ko, C.; Lee, Y.; Chen, Y.; Suh, J.; Fu, D.; Suslu, A.; Lee, S.; Clarkson, J. D.; Choe, H. S.; Tongay, S.; Ramesh, R.; Wu, J. Ferroelectrically Gated Atomically Thin Transition-Metal Dichalcogenides as Nonvolatile Memory. *Adv. Mater.* **2016**, *28*, 2923–2930.

- (13) Lu, Z.; Serrao, C.; Khan, A. I.; You, L.; Wong, J. C.; Ye, Y.; Zhu, H.; Zhang, X.; Salahuddin, S. Nonvolatile MoS<sub>2</sub> Field Effect Transistors Directly Gated by Single Crystalline Epitaxial Ferroelectric. *Appl. Phys. Lett.* **2017**, *111*, 023104.

- (14) Yap, W. C.; Jiang, H.; Liu, J.; Xia, Q.; Zhu, W. Ferroelectric Transistors with Monolayer Molybdenum Disulfide and Ultra-thin Aluminum-doped Hafnium Oxide. *Appl. Phys. Lett.* **2017**, *111*, 013103.

- (15) Nourbakhsh, A.; Zubair, A.; Joglekar, S. J.; Dresselhaus, M. S.; Palacios, T. Subthreshold Swing Improvement in MoS<sub>2</sub> Transistors by the Negative-Capacitance Effect in a Ferroelectric Al-doped-HfO<sub>2</sub>/HfO<sub>2</sub> Gate Dielectric Stack. *Nanoscale* **2017**, *9*, 6122–6127.

- (16) McGuire, F. A.; Lin, Y.-C.; Price, K.; Rayner, G. B.; Khandelwal, S.; Salahuddin, S.; Franklin, A. D. Sustained Sub-60 mV/decade Switching *via* the Negative Capacitance Effect in MoS<sub>2</sub> Transistors. *Nano Lett.* **2017**, *17*, 4801–4806.

- (17) Yu, Z.; Wang, H.; Li, W.; Xu, S.; Song, X.; Wang, S.; Wang, P.; Zhou, P.; Shi, Y.; Chai, Y.; Wang, X. Negative Capacitance 2D  $MoS_2$  Transistors with Sub-60mV/dec Subthreshold Swing over 6 Orders, 250  $\mu$ A/ $\mu$ m Current Density, and Nearly-Hysteresis-Free. *Proc. IEEE Int. Electron. Dev. Meet.* **2017**, 577–580.

(18) Si, M.; Jiang, C.; Su, C.-J.; Tang, Y.-T.; Yang, L.; Chung, W.; Alam, M. A.; Ye, P. D. Sub-60 mV/dec Ferroelectric HZO MoS<sub>2</sub> Negative Capacitance Field-Effect Transistor with Internal Metal Gate: the Role of Parasitic Capacitance. *Proc. IEEE Int. Electron. Dev. Meet.* 2017, 573–576.

- (19) Wang, X.; Chen, Y.; Wu, G.; Li, D.; Tu, L.; Sun, S.; Shen, H.; Lin, T.; Xiao, Y.; Tang, M.; Hu, W.; Liao, L.; Zhou, P.; Sun, J.; Meng, X.; Chu, J.; Wang, J. Two-Dimensional Negative Capacitance Transistor with Polyvinylidene Fluoride-based Ferroelectric Polymer Gating. npj 2D Mater. Appl. 2017, 1, 38.

- (20) Si, M.; Su, C.-J.; Jiang, C.; Conrad, N. J.; Zhou, H.; Maize, K. D.; Qiu, G.; Wu, C.-T.; Shakouri, A.; Alam, M. A.; Ye, P. D. Steep-Slope Hysteresis-Free Negative Capacitance MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2018**, *13*, 24–29.

- (21) Liu, H.; Ye, P. D. MoS<sub>2</sub> Dual-Gate MOSFET with Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> as Top-Gate Dielectric. *IEEE Electron Device Lett.* **2012**, 33, 546–548.

- (22) Dawber, M.; Rabe, K. M.; Scott, J. F. Physics of Thin-Film Ferroelectric Oxides. *Rev. Mod. Phys.* **2005**, *77*, 1083–1130.

- (23) Ding, W.; Zhu, J.; Wang, Z.; Gao, Y.; Xiao, D.; Gu, Y.; Zhang, Z.; Zhu, W. Prediction of Intrinsic Two-Dimensional Ferroelectrics in In<sub>2</sub>Se<sub>3</sub> and Other III<sub>2</sub>-VI<sub>3</sub> Van der Waals Materials. *Nat. Commun.* **2017**, *8*, 14956.

- (24) Wan, W.; Liu, C.; Xiao, W.; Yao, Y. Promising Ferroelectricity in 2D group IV Tellurides: A First-Principles Study. *Appl. Phys. Lett.* **2017**, *111*, 132904.

- (25) Chandrasekaran, A.; Mishra, A.; Singh, A. K. Ferroelectricity, Antiferroelectricity, and Ultrathin 2D Electron/Hole Gas in Multifunctional Monolayer MXene. *Nano Lett.* **2017**, *17*, 3290–3296.

- (26) Wang, H.; Qian, X. Two-dimensional Multiferroics in Monolayer Group IV Monochalcogenides. 2D Mater. 2017, 4, 015042.

- (27) Liu, F.; You, L.; Seyler, K. L.; Li, X.; Yu, P.; Lin, J.; Wang, X.; Zhou, J.; Wang, H.; He, H.; Pantelides, S. T.; Zhou, W.; Sharma, P.; Xu, X.; Ajayan, P. M.; Wang, J.; Liu, Z. Room-Temperature Ferroelectricity in CuInP<sub>2</sub>S<sub>6</sub> Ultrathin Flakes. *Nat. Commun.* **2016**, 7, 12357.

- (28) Zhou, Y.; Wu, D.; Zhu, Y.; Cho, Y.; He, Q.; Yang, X.; Herrera, K.; Chu, Z.; Han, Y.; Downer, M. C.; Peng, H.; Lai, K. Out-of-Plane Piezoelectricity and Ferroelectricity in Layered  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> Nanoflakes. *Nano Lett.* **2017**, *17*, 5508–5513.

- (29) Cui, C.; Hu, W.-J.; Yan, X.; Addiego, C.; Gao, W.; Wang, Y.; Wang, Z.; Li, L.; Cheng, Y.; Li, P.; Zhang, X.; Alshareef, H. N.; Wu, T.; Zhu, W.; Pan, X.; Li, L.-J. Intercorrelated In-Plane and Out-of-Plane Ferroelectricity in Ultrathin Two-Dimensional Layered Semi-conductor In<sub>2</sub>Se<sub>3</sub>. *Nano Lett.* **2018**, *18*, 1253–1258.

- (30) Belianinov, A.; He, Q.; Dziaugys, A.; Maksymovych, P.; Eliseev, E.; Borisevich, A.; Morozovska, A.; Banys, J.; Vysochanskii, Y.; Kalinin, S. V. CuInP<sub>2</sub>S<sub>6</sub> Room Temperature Layered Ferroelectric. *Nano Lett.* **2015**, *15*, 3808–3814.

- (31) Maisonneuve, V.; Cajipe, V.; Simon, A.; Von Der Muhll, R.; Ravez, J. Ferrielectric Ordering in Lamellar CuInP<sub>2</sub>S<sub>6</sub>. *Phys. Rev. B: Condens. Matter Mater. Phys.* **1997**, *56*, 10860–10868.

- (32) Maisonneuve, V.; Évain, M.; Payen, C.; Cajipe, V. B.; Molinié, P. Room-temperature Crystal Structure of the Layered Phase Cu<sup>I</sup>n<sup>III</sup>P<sub>2</sub>S<sub>6</sub>. J. Alloys Compd. **1995**, 218, 157–164.

- (33) Vysochanskii, Y. M.; Stephanovich, V.; Molnar, A.; Cajipe, V.; Bourdon, X. Raman Spectroscopy Study of the Ferrielectric-Paraelectric Transition in Layered CuInP<sub>2</sub>S<sub>6</sub>. *Phys. Rev. B: Condens. Matter Mater. Phys.* **1998**, 58, 9119–9124.

- (34) Wang, C.; Jin, K.; Xu, Z.; Wang, L.; Ge, C.; Lu, H.; Guo, H.; He, M.; Yang, G. Switchable Diode Effect and Ferroelectric Resistive Switching in Epitaxial BiFeO<sub>3</sub> Thin Films. *Appl. Phys. Lett.* **2011**, 98, 192901.

- (35) Castellanos-Gomez, A.; Buscema, M.; Molenaar, R.; Singh, V.; Janssen, L.; Van der Zant, H. S. J.; Steele, G. A. Deterministic Transfer of Two-Dimensional Materials by All-Dry Viscoelastic Stamping. 2D Mater. 2014, 1, 011002.