# Universal PBTI Relaxation on the Negative V<sub>TH</sub> Shift in Oxide Semiconductor Transistors and New Insights

Zhiyu Lin, Jinxiu Zhao<sup>®</sup>, Xiuyan Li, *Member, IEEE*, Lu Kang, Junkang Li, Ying Wu, Jeffrey Xu, and Mengwei Si<sup>®</sup>, *Member, IEEE*

Abstract—In this work, the positive bias temperature instability (PBTI) degradation of ZnO transistors by atomic layer deposition (ALD) is systematically investigated by using an extended measure-stress-measure (eMSM) technique. We observe for the first time the anomalous negative threshold voltage (V<sub>TH</sub>) shift under PBTI stress, which is frequently observed in oxide semiconductor transistors, can be well described by a universal relaxation model. The permanent component (P) and recoverable component (R) are simultaneously extracted, clearly showing that the R component is dominated by negative V<sub>TH</sub> shift while P component is positive. The universality of PBTI relaxation on the negative  $V_{TH}$  shift in oxide semiconductors suggests hydrogen (H) transport may play a key role on understanding PBTI degradation phenomenon in oxide semiconductor devices, and relaxation must be considered for accurate evaluation of lifetime.

Index Terms—Atomic layer deposition, zinc oxide, positive bias temperature instability, thin-film transistor.

## I. INTRODUCTION

**O** XIDE semiconductor transistors have been increasingly appealing as back-end-of-line (BEOL) compatible transistors for monolithic 3D integration. Oxide semiconductor transistors have been demonstrated with encouraging performance such as high drive current, steep subthreshold slope (SS), ultra-low off-state leakage current and BEOL compatibility [1], [2], [3], [4], [5], [6], [7], [8], [9]. To integrate

Manuscript received 10 April 2023; revised 4 May 2023; accepted 6 May 2023. Date of publication 10 May 2023; date of current version 28 June 2023. This work was supported in part by the National Key Research and Development Program of China under Grant 2022YFB3606900, in part by the Shanghai Pilot Program for Basic Research-Shanghai Jiao Tong University under Grant 21TQ1400212, and in part by the National Natural Science Foundation of China under Grant 62274107 and Grant 92264204. The review of this letter was arranged by Editor M. Kobayashi. (*Corresponding author: Mengwei Si.*)

Zhiyu Lin, Jinxiu Zhao, and Mengwei Si are with the Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China (e-mail: mengwei.si@sjtu.edu.cn).

Xiuyan Li is with the Department of Nano/Micro-Electronics, Shanghai Jiao Tong University, Shanghai 200240, China.

Lu Kang, Junkang Li, Ying Wu, and Jeffrey Xu are with Huawei Technologies Company Ltd., Shenzhen 518063, China.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2023.3274771.

Digital Object Identifier 10.1109/LED.2023.3274771

oxide semiconductor devices with Si CMOS, the reliability performance remains critical. There have been studies on the BTI degradation of scaled oxide semiconductor devices for BEOL, showing decent BTI performance but much more complex than Si metal-oxide-semiconductor field-effect transistors (MOSFETs), such as negative threshold voltage  $(V_{TH})$  shift under positive bias temperature instability (PBTI) stress [10], [11], [12], [13], [14]. How to properly understand the degradation mechanisms under BTI stress in oxide semiconductor transistors is still not clear.

In this work, ZnO transistor by atomic layer deposition (ALD) is used as a model system to study the PBTI degradation in oxide semiconductor transistors. An extended measure-stress-measure (eMSM) technique is adopted to capture both permanent component (P) and recoverable component (R) during PBTI measurements [15]. It is found that the anomalous negative  $V_{TH}$  shift under PBTI stress can be well described by a universal relaxation model. The R component is dominated by negative  $V_{TH}$  shift while P component is positive. The universality of PBTI relaxation on the negative  $V_{TH}$  shift suggests PBTI degradation in oxide semiconductor transistors may be strongly related with reaction and diffusion (RD) of hydrogen (H).

### **II.** EXPERIMENTS

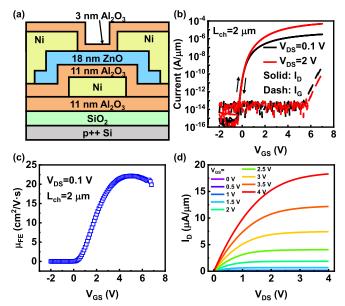

The schematic diagram of ALD ZnO transistors in this work is shown in Fig. 1(a). 11 nm Al<sub>2</sub>O<sub>3</sub> was used as gate insulator and 18 nm ZnO was used as channel. Ni was used for both gate metal and source/drain (S/D) contacts. The fabrication process is similar to previous work in [16]. 3 nm Al<sub>2</sub>O<sub>3</sub> passivation layer by ALD at 200°C was used to prevent reaction with oxygen and moisture in air. The devices were annealed in air at 250°C for 1 minute after passivation in order to heal the damage in oxide semiconductor during passivation layer growth process. The overall thermal budget was controlled under 250°C. All electrical measurements were done on devices with passivation unless otherwise specified.

## **III. RESULTS AND DISCUSSION**

Fig. 1(b) shows the transfer characteristics of ZnO transistor with channel length  $(L_{ch})$  of 2  $\mu$ m, showing negligible hysteresis and SS of 91.5 mV/dec. Fig. 1(c) presents the

0741-3106 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Authorized licensed use limited to: Shanghai Jiaotong University. Downloaded on July 20,2023 at 05:24:51 UTC from IEEE Xplore. Restrictions apply.

Fig. 1. (a) Schematic diagram of a passivated ALD ZnO transistor. (b) Transfer characteristics, (c)  $\mu_{FE}$  versus  $V_{GS}$  extracted from transfer curve at  $V_{DS} = 0.1$  V, and (d) output characteristics of a typical ZnO transistor with  $L_{ch} = 2\mu$ .

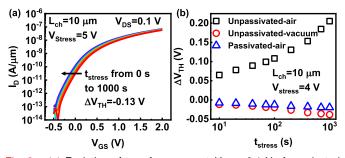

Fig. 2. (a) Evolution of transfer curves at  $V_{DS} = 0.1$  V of passivated ZnO transistor with  $L_{ch} = 10 \ \mu \text{m}$  under  $V_{stress}$  of 5 V and  $t_{stress}$  from 0 s to 1000 s. (b)  $V_{TH}$  under PBTI stress extracted from transfer curves of unpassivated device tested in air and vacuum, and passivated device tested in air.

field-effect mobility ( $\mu_{FE}$ ) extracted from transfer curve at  $V_{DS} = 0.1$  V. The corresponding output characteristics of ZnO transistor are shown in Fig. 1(d). Electrical performance of ZnO transistors without 3 nm Al<sub>2</sub>O<sub>3</sub> passivation was reported in our previous work in [16], which is similar to those with 3 nm Al<sub>2</sub>O<sub>3</sub> passivation in this work in terms of DC performance.

Fig. 2(a) shows the evolution of transfer characteristics of passivated ZnO transistor under PBTI stress.  $V_{TH}$  shifts negatively during PBTI stress, as commonly observed in oxide semiconductor devices [12], [13], [17]. SS remains nearly unchanged during stress, indicating  $V_{TH}$  shift under PBTI stress is minorly affected by interface trap generation. The impact of passivation on PBTI degradation of ZnO transistors is studied in Fig. 2(b). A large positive  $V_{TH}$  shift is observed in unpassivated device stressed in air, indicating that ZnO interacts with oxygen and moisture during PBTI stress and contribute to a positive  $V_{TH}$  shift, most likely because of the reduction of oxygen vacancy and carrier density. This also suggests the negative  $V_{TH}$  shift under PBTI stress is not related with top interface of ZnO.

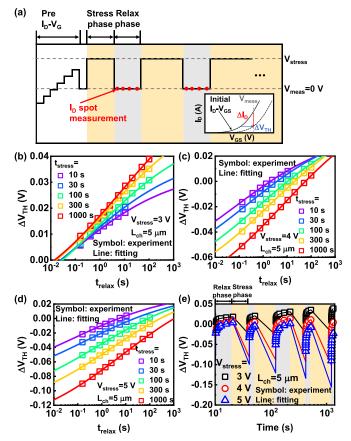

Fig. 3. (a) Schematic of eMSM measurement method. At relax phase  $I_D$  spot measurements at  $V_{DS} = 0.1$  V are performed from  $t_{relax} = 0.1$  s to 100 s. Inset:  $V_{TH}$  extraction method from  $I_D$  spot measurement.  $V_{TH}$  versus  $t_{relax}$  under  $V_{stress}$  of (b) 3 V, (c) 4 V and (d) 5 V for different  $t_{stress}$ . Experimental data is fitted by universal relaxation model. (e)  $V_{TH}$  versus total time under different  $V_{stress}$ , clearly showing a positive P component and a negative R component.

To further study the degradation mechanisms under PBTI stress, eMSM scheme was applied to distinguish the *P* component and *R* component [15]. Schematic of eMSM method in this work is illustrated in Fig. 3(a), as has been developed in [15]. The eMSM measurement started with a pre  $I_D$ - $V_{GS}$  sweep before stress. Then, a stress voltage ( $V_{stress}$ ) was applied to  $V_{GS}$  for different stress time ( $t_{stress}$ ). After each stress phase  $V_{GS}$  switched to 0 V as relax phase and multi-spot  $I_D$  was measured during relaxation time ( $t_{relax}$ ) of 0.1 s to 100 s, to capture the relaxation properties. The procedure on  $\Delta V_{TH}$  extraction is illustrated in inset of Fig. 3(a).

The BTI relaxation of traditional Si MOSFETs is wellknown to follow a universal relaxation function that  $r(\xi)=1/(1+B\xi^{\beta})$ , where  $\xi=t_{relax}/t_{stress}$ , *B* is a scaling parameter and  $\beta$  is a dispersion parameter. The *R* component and *P* component can be described by  $\Delta V_{TH}(t_{sress}, t_{relax})=P(t_{stress})+R(t_{sress}, t_{relax})$  and  $R(t_{sress}, t_{relax})=R(t_{sress}, t_{relax}=0)r(\xi)$ . Although the universality of BTI relaxation is well-established in Si MOSFETs related with H transport [18], it is unclear whether such universality exists in oxide semiconductor transistors. Note that,  $\Delta V_{TH}$  under PBTI stress can be negative for oxide semiconductor devices, as shown in Fig. 2(a), so that the stress and recover process in oxide semiconductors can be very different from Si case.

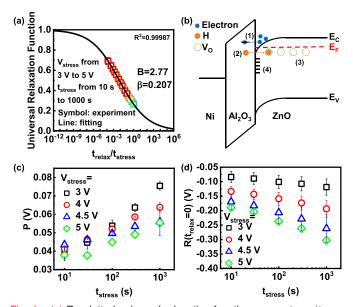

Fig. 4. (a) Re-plotted universal relaxation function versus  $t_{relax}/t_{stress}$  under different  $V_{stress}$  and  $t_{stress}$ . (b) Illustration of degradation mechanisms during PBTI stress. (c) Permanent component P and (d) recoverable component R versus  $t_{stress}$  at different  $V_{stress}$  extracted by universal relaxation model.

Fig. 3(b)-(d) show  $\Delta V_{TH}$  versus  $t_{relax}$  at different  $t_{stress}$ under V<sub>stress</sub> of 3 V, 4 V, and 5 V. At a low V<sub>stress</sub> of 3 V, a positive  $V_{TH}$  shift is observed after stress phase but during the relax phase  $V_{TH}$  shifts positively, suggesting that the negative  $V_{TH}$  shift under PBTI stress is recoverable. At a higher  $V_{stress}$  of 4 V or 5 V,  $V_{TH}$  shifts negatively and recovers positively. The universal BTI relaxation function  $\Delta V_{TH}(t_{sress},$  $t_{relax}$  =  $P(t_{stress}) + R(t_{sress}, t_{relax} = 0)/(1 + B\xi^{\beta})$  is used to fit the experimental data to extract P, R, B, and  $\beta$ , as shown in the lines in Fig. 3(b)-(d), extracting a positive P component and negative R component, which explains the positive/negative  $V_{TH}$  shift under different  $V_{stress}$ , as also plotted in total time scale in Fig. 3(e). For example, at  $V_{stress}$  of 3 V,  $\Delta V_{TH}$  is positive after stress phase and becomes larger during recover phase, which is different from at  $V_{stress}$  of 4 V and 5 V, because the absolute value of negative R component is only slightly larger than positive P component at low  $V_{stress}$ , and after a detectable measurement delay of about 120 ms the remanent R component become smaller than P. At high  $V_{stress}$ , P component becomes much smaller than the negative R component. Thus, P and R components under PBTI have different voltage dependence.

The data in Fig. 3(b)-(d) is re-plotted using  $t_{relax}/t_{stress}$  as x-axis and  $r(\xi)$  as y-axis, as shown in Fig. 4(a).  $R^2$  equals to 0.99987 indicating that the experimental data fit surprisingly well with the universal BTI relaxation model. The extracted *B* and  $\beta$  are similar to results in Si MOSFETs [18]. Therefore, we confirm that the negative  $V_{TH}$  shift under PBTI stress in oxide semiconductors transistors follows the universal BTI relaxation function.

Fig. 4(b) illustrates possible degradation mechanisms under PBTI stress, including 1) electron trapping/de-trapping, 2) H reaction and diffusion, 3) oxygen vacancies (V<sub>O</sub>) generation, 4) interface trap generation. The two possible mechanisms lead to negative  $V_{TH}$  shift are H reaction and diffusion and V<sub>O</sub> generation, since H and  $V_0$  are electron donors for oxide semiconductors. We speculate trap generation more likely contribute to *P* component since trap is a slower process. Meanwhile, it is well-known universal BTI relaxation in Si MOSFET is related with H transport [18]. Thus, the negative  $V_{TH}$  shift under PBTI stress in oxide semiconductor transistors most likely originates from H reaction and diffusion.

*P* and *R* components versus  $t_{stress}$  at different  $V_{stress}$  are summarized in Fig. 4(c) and Fig. 4(d). *P* components at different  $V_{stress}$  are positive while *R* components are negative. *R* components show strong  $V_{stress}$  dependence and the absolute values of *R* are larger than *P*. *P* components show no obvious dependence on  $V_{stress}$ , indicating that there might be multiple competing mechanisms on permanent degradation. For example, there may exist both donor trap generation and accept trap generation under PBTI, contributing to both positive and negative *P* components. The absolute values of *P* are all less than 100 mV even at high voltages, suggesting the ALD ZnO transistors has high PBTI stability.

## **IV. CONCLUSION**

In summary, the anomalous negative  $V_{TH}$  shift under PBTI stress in oxide semiconductor transistors, is found to be welldescribed by a universal relaxation model. The *R* component is dominated by such negative  $V_{TH}$  shift while *P* component is positive. The universality of PBTI relaxation on the negative  $V_{TH}$  shift provides new insights to understand the PBTI degradation of oxide semiconductor devices, which suggests H transport may play a key role during PBTI degradation.

## REFERENCES

- [1] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Nov. 2004, doi: 10.1038/nature03090.

- [2] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with I<sub>on</sub> = 370  $\mu$ A/ $\mu$ m, SS = 73 mV/dec and I<sub>on</sub>/I<sub>off</sub> ratio >  $4 \times 10^9$ ," in *Proc. Symp. VLSI Technol.*, Jun. 2020, pp. 1–2, Paper TH2.1, doi: 10.1109/VLSITECHNOLOGY18217.2020.9265064.

- [3] J. Wu, F. Mo, T. Saraya, T. Hiramoto, M. Ochi, H. Goto, and M. Kobayashi, "Mobility-enhanced FET and wakeup-free ferroelectric capacitor enabled by Sn-doped InGaZnO for 3D embedded RAM application," in *Proc. Symp. VLSI Technol.*, Jun. 2021, pp. 1–2, Paper T6-2.

- [4] M. Wang, D. Zhan, X. Wang, Q. Hu, C. Gu, X. Li, and Y. Wu, "Performance optimization of atomic layer deposited ZnO thin-film transistors by vacuum annealing," *IEEE Electron Device Lett.*, vol. 42, no. 5, pp. 716–719, May 2021, doi: 10.1109/LED.2021.3068992.

- [5] M. Si, Z. Lin, Z. Chen, X. Sun, H. Wang, and P. D. Ye, "Scaled indium oxide transistors fabricated using atomic layer deposition," *Nature Electron.*, vol. 5, no. 3, pp. 164–170, Feb. 2022, doi: 10.1038/s41928-022-00718-w.

- [6] C. Wang, A. Kumar, K. Han, C. Sun, H. Xu, J. Zhang, Y. Kang, Q. Kong, Z. Zheng, Y. Wang, and X. Gong, "Extremely scaled bottom gate a-IGZO transistors using a novel patterning technique achieving record high G<sub>m</sub> of 479.5 μS/μm (V<sub>DS</sub> of 1 V) and f<sub>T</sub> of 18.3 GHz (V<sub>DS</sub> of 3 V)," in *Proc. Symp. VLSI Technol.*, Jun. 2022, pp. 294–295, Paper T02-2, doi: 10.1109/VLSITECHNOLOGYAND-CIR46769.2022.9830393.

- [7] J. Lee, C. H. Choi, T. Kim, J. Hur, M. J. Kim, E. H. Kim, J. H. Lim, Y. Kang, and J. K. Jeong, "Hydrogen-doping-enabled boosting of the carrier mobility and stability in amorphous IGZTO transistors," ACS Appl. Mater. Interfaces, vol. 14, no. 51, pp. 57016–57027, Dec. 2022, doi: 10.1021/acsami.2c18094.

- [8] W. Lu, Z. Zhu, K. Chen, M. Liu, B.-M. Kang, X. Duan, J. Niu, F. Liao, W. Dan, X.-S. Wu, J. Son, D.-Y. Xiao, G.-L. Wang, A. Yoo, K.-Y. Cao, D. Geng, N. Lu, G. Yang, C. Zhao, L. Li, and M. Liu, "First demonstration of dual-gate IGZO 2TOC DRAM with novel read operation, one bit line in single cell, I<sub>ON</sub>=1500 μA/μm@V<sub>DS</sub>=1 V and retention time>300s," in *IEDM Tech. Dig.*, Dec. 2022, pp. 611–614, doi: 10.1109/IEDM45625.2022.10019488.

- [9] W. Lu, C. Lu, G. Yang, M. Liu, K. Chen, F. Liao, X. Duan, N. Lu, and L. Li, "Monolithically stacked two layers of a-IGZObased transistors upon a-IGZO-based analog/logic circuits," *IEEE Trans. Electron Devices*, vol. 70, no. 4, pp. 1697–1701, Apr. 2023, doi: 10.1109/TED.2023.3247364.

- [10] A. Chasin, J. Franco, K. Triantopoulos, H. Dekkers, N. Rassoul, A. Belmonte, Q. Smets, S. Subhechha, D. Claes, M. J. van Setten, J. Mitard, R. Delhougne, V. Afanas'ev, B. Kaczer, and G. S. Kar, "Understanding and modelling the PBTI reliability of thin-film IGZO transistors," in *IEDM Tech. Dig.*, Dec. 2021, pp. 657–660, doi: 10.1109/IEDM19574.2021.9720666.

- [11] Y.-S. Shiah, K. Sim, Y. Shi, K. Abe, S. Ueda, M. Sasase, J. Kim, and H. Hosono, "Mobility-stability trade-off in oxide thin-film transistors," *Nature Electron.*, vol. 4, no. 11, pp. 800–807, Nov. 2021, doi: 10.1038/s41928-021-00671-0.

- [12] D. Zheng, A. Charnas, J. Anderson, H. Dou, Z. Hu, Z. Lin, Z. Zhang, J. Zhang, P.-Y. Liao, M. Si, H. Wang, D. Weinstein, and P. D. Ye, "First demonstration of BEOL-compatible ultrathin atomiclayer-deposited InZnO transistors with GHz operation and record high bias-stress stability," in *IEDM Tech. Dig.*, Dec. 2022, pp. 78–81, doi: 10.1109/IEDM45625.2022.10019452.

- [13] Q. Kong, G. Liu, C. Sun, Z. Zheng, D. Zhang, J. Zhang, H. Xu, L. Liu, Z. Zhou, L. Jiao, X. Wang, K. Han, Y. Kang, B.-Y. Nguyen, K. Ni, and X. Gong, "New insights into the impact of hydrogen evolution on the reliability of IGZO FETs: Experiment and modeling," in *IEDM Tech. Dig.*, Dec. 2022, pp. 699–702, doi: 10.1109/IEDM45625.2022.10019394.

- [14] Z. Wu, A. Chasin, J. Franco, S. Subhechha, H. Dekkers, Y. V. Bhuvaneshwari, A. Belmonte, N. Rassoul, M. J. van Setten, V. Afanas'ev, R. Delhougne, B. Kaczer, and G. S. Kar, "Characterizing and modelling of the BTI reliability in IGZO-TFT using light-assisted I-V spectroscopy," in *IEDM Tech. Dig.*, Dec. 2022, pp. 695–698, doi: 10.1109/IEDM45625.2022.10019454.

- [15] B. Kaczer, T. Grasser, J. Roussel, J. Martin-Martinez, R. O'Connor, B. J. O'Sullivan, and G. Groeseneken, "Ubiquitous relaxation in BTI stressing—New evaluation and insights," in *Proc. IEEE Int. Rel. Phys. Symp.*, Apr. 2008, pp. 20–27, doi: 10.1109/RELPHY.2008.4558858.

- [16] Z. Lin, Z. Wang, J. Zhao, X. Li, and M. Si, "A low-leakage zinc oxide transistor by atomic layer deposition," *IEEE Electron Device Lett.*, vol. 44, no. 3, pp. 536–539, Mar. 2023, doi: 10.1109/LED.2022.3233943.

- [17] J. Zhang, D. Zheng, Z. Zhang, A. Charnas, Z. Lin, and P. D. Ye, "Ultrathin InGaO thin film transistors by atomic layer deposition," *IEEE Electron Device Lett.*, vol. 44, no. 2, pp. 273–276, Feb. 2023, doi: 10.1109/LED.2022.3233080.

- [18] B. Kaczer, T. Grasser, R. Fernandez, and G. Groeseneken, "Toward understanding the wide distribution of time scales in negative bias temperature instability," *ECS Trans.*, vol. 6, no. 3, pp. 265–281, Apr. 2007, doi: 10.1149/1.2728801.