ELSEVIER

Contents lists available at ScienceDirect

### Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

## Enhanced electrical performances with HZO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 3D FinFET toward highly perceptual synaptic device application

Seohyeon Park <sup>a,1</sup>, Jaewook Yoo <sup>a,1</sup>, Seokjin Oh <sup>i</sup>, Hongseung Lee <sup>a</sup>, Minah Park <sup>a</sup>, Seongbin Lim <sup>a</sup>, Soyeon Kim <sup>a</sup>, Sojin Jung <sup>a</sup>, Bongjoong Kim <sup>h</sup>, Keun Heo <sup>g</sup>, Taehwan Moon <sup>f</sup>, TaeWan Kim <sup>d,e</sup>, Mengwei Si <sup>c</sup>, Peide D. Ye <sup>b</sup>, Hagyoul Bae <sup>a,\*</sup> <sup>©</sup>

- <sup>a</sup> Department of Electronic Engineering, Jeonbuk National University, 567 Baekje-daero, Deokjin-gu, Jeonju, 54896, Republic of Korea

- <sup>b</sup> School of Electrical and Computer Engineering, Purdue University, 465 Northwestern Ave., West Lafayette, IN, 47907, USA

- <sup>c</sup> Department of Electronic Engineering, Shanghai Jiao Tong University, 800 Dongchuan Road, Minhang, Shanghai, 200240, China

- d Department of Intelligent Semiconductor Engineering and School of Advanced Fusion Studies, University of Seoul, Seoul, 02504, Republic of Korea

- <sup>e</sup> 2D Epi, inc, Jeonju, 54896, Republic of Korea

- f Department of Intelligence Semiconductor Engineering, Ajou University, Suwon, 16499, Republic of Korea

- g School of Semiconductor Science and Technology, Jeonbuk National University, 567 Baekje-daero, Deokjin-gu, Jeonju 54896, Republic of Korea

- <sup>h</sup> Department of Mechanical & System Design Engineering, Hongik University, Seoul, 04066, Republic of Korea

- <sup>i</sup> School of Electrical Engineering, Kookmin University, Seoul, 02707, Republic of Korea

#### ARTICLE INFO

# Keywords: Beta-gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) Ultrawide bandgap (UWBG) Hafnium zirconium oxide (HZO) Ferroelectric fin field-effect transistor (Fe-Fin-FET) Non-volatile memory device Synaptic

#### ABSTRACT

In this study, we have demonstrated a novel high-performance ferroelectric FinFET (Fe-FinFET) that integrates ultra-wide-bandgap (UWBG) beta-gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) channel with an atomic layer deposited (ALD) hafnium zirconium oxide (HZO) ferroelectric layer for the first time, and experimentally validated the effectiveness of the robust  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> platform as a memory application. Compared with conventional planar ferroelectric FET (FeFET), the Fe-FinFET exhibits a markedly wider counter-clockwise hysteresis loop in its transfer characteristics, achieving a large memory window (MW) of 13.9 V with a single HZO layer. When normalized to the actual channel width, the Fe-FinFETs show an improved  $I_{\text{ON}}/I_{\text{OFF}}$  ratio of  $2.3 \times 10^7$  and a subthreshold swing value of 110 mV/dec; Y-function method further indicates that the intrinsic mobility is improved to  $4.25 \times 10^2$ cm<sup>2</sup>/Vs. The enhanced polarization due to larger electric fields across the ferroelectric layer in Fe-FinFET is validated using Sentaurus TCAD, and this result is further supported by the energy-dependent distribution of interface trap density  $(D_{it})$  extracted in both forward and reverse sweep directions. After  $5 \times 10^6$  program/erase (PGM/ERS) cycles, the MW was maintained at 9.2 V, and the retention time was measured up to  $3 \times 10^4$  s with low degradation. To verify its potential as an artificial synapse, we trained a convolutional neural network (CNN) and achieved an accuracy of 91.7 %. These results establish the HZO/β-Ga<sub>2</sub>O<sub>3</sub> Fe-FinFET as a promising candidate for high voltage-enduring, non-volatile memory devices that also offer synaptic functionality for neuromorphic applications.

#### 1. Introduction

As silicon-based transistors approach their ultimate scaling limits, the search for alternative channel materials and device architectures has become essential [1,2]. Semiconductors classified as ultrawide bandgap (UWBG) including gallium nitride (GaN), silicon carbide (SiC), and beta-gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) provide distinct advantages over silicon-based devices, enabling for smaller, faster, and more efficient

electronics, especially when high voltages, high frequencies, or elevated temperatures are involved [3]. Among these UWBG materials,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is considered the only material capable of single-crystal mass growth from the early stages of development [4].

Monolithic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with a UWBG of 4.6–4.9 eV has been identified as an emerging candidate for next-generation electronic devices. Its UWBG property enables the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material to have high breakdown electric fields, high carrier mobility, and sustainability under large

$<sup>^{\</sup>star}$  Corresponding author.

E-mail address: hagyoul.bae@jbnu.ac.kr (H. Bae).

Seohyeon Park and Jaewook Yoo contributed equally.

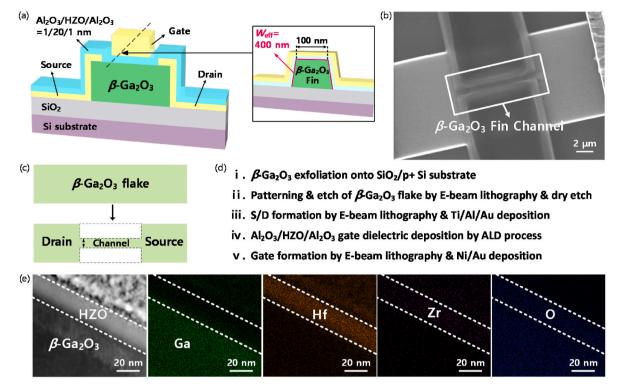

Fig. 1. (a) Schematic of HZO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Fe-FinFET. (b) SEM image of the fabricated 3D fin structure after RIE etching process. (c) Top-view schematic of fin-structure patterning. (d) Key process steps of device fabrication. (e) TEM images of fabricated HZO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers and EDS elemental mapping with scanning TEM images of Ga, Hf, Zr, and O.

electric fields, high power, and high operating temperatures [5–11].  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with these properties is particularly attractive for electronic devices exhibiting high-voltage operation in harsh environments [12–14].

Meanwhile, hafnium zirconium oxide (HZO) has shown ferroelectric behavior at high temperatures. The HZO layer is a promising component because it is compatible with complementary metal-oxide-semiconductor (CMOS) in back-end-of-line (BEOL) thermal budget (<400 °C) and exhibits strong ferroelectricity even at very thin thickness (<10 nm) [15–18]. These properties make HZO applicable to various devices, including ferroelectric field-effect transistor (FeFET), ferroelectric random-access memory (FeRAM), and ferroelectric tunnel junction memory (FTJ) [19,20]. FeFETs have been highlighted for their ability to be manufactured simply by inserting a ferroelectric film into the gate stack of a conventional MOSFET. Therefore, FeFETs can exhibit non-volatile memory behaviors while maintaining the same footprint as traditional FETs.

Accordingly, ferroelectric UWBG semiconductor devices have the potential to fill the need for robust electrical operation of neuromorphic applications. A  $\rm HZO/\beta\text{-}Ga_2O_3$  planar FeFET achieved high on-chip learning accuracy at high temperatures, with improved electrical performance [21].

From a channel-architecture perspective, three-dimensional devices such as FinFET have already demonstrated aggressive scaling and clear performance improvements through numerous prior studies. Nevertheless, experimental studies on ferroelectric UWBG FinFETs are still lacking, leaving their potential performance gains, long-term reliability, and potential for neuromorphic applications unexplored.

In this work, HZO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> ferroelectric FinFET (Fe-FinFET) with a fin width of 100 nm was fabricated. The fabricated Fe-FinFET presented robust electrical performances with accelerated electric dipole switching, high  $I_{ON}/I_{OFF}$  ratio, steep subthreshold swing (SS), and large memory window (MW) compared with planar FeFET. TCAD simulation indicated enhanced electric fields in the ferroelectric layer of the Fe-

FinFET, a finding that is consistent with the sweep-direction-dependent energy distribution of interface trap density ( $D_{\rm it}$ ). Furthermore, this study demonstrated significantly improved retention time and endurance, and 91.7 % accuracy in a CNN simulation using the CIFAR-10 dataset, for high reliability and expandability to memory devices in the neuromorphic field. The wide bandgap and stable conductivity of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel effectively support HZO polarization switching, thereby contributing to the realization of stable and reliable memory operation.

#### 2. Device fabrication

Fig. 1 (a) shows the cross-sectional view of the manufactured device along both channel width and length directions. For fabrication of the HZO/β-Ga<sub>2</sub>O<sub>3</sub> Fe-FinFETs, thin nanomembrane flakes were realized by cleaving the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> bulk substrate into small pieces and employing a mechanical exfoliation technique with adhesive tape [18]. The exfoliated flake with a thickness of 130 nm was transferred onto a 270 nm SiO<sub>2</sub>/p + type Si substrate. Photoresist (PR) was then applied, and electron beam lithography (EBL) was used for fin patterning, followed by development. Dry etching was performed to create a fin-structured channel. Source and drain electrodes were patterned by EBL, Fig. 1 (b) shows the scanning electron microscope (SEM) image of an etched β-Ga<sub>2</sub>O<sub>3</sub> channel with a width of 100 nm. Before metallization, an Ar plasma bombardment with a radio frequency power of 100 W was applied to improve the contact resistance (R<sub>C</sub>) by generating oxygen vacancies to enhance the surface of β-Ga<sub>2</sub>O<sub>3</sub> flakes. Ti/Al/Au (15/60/50 nm) metal electrodes were deposited using electron beam evaporation and the lift-off process. A ferroelectric HZO gate stack of Al<sub>2</sub>O<sub>3</sub>/H-ZO/Al<sub>2</sub>O<sub>3</sub> (1/20/1.

nm) was deposited by the atomic layer deposition (ALD) process. Applying the 1 nm amorphous  $Al_2O_3$  layer on the bottom of the stack achieved better interface quality, and the top  $Al_2O_3$  was deposited to avoid degradation of the HZO layer by reaction with other

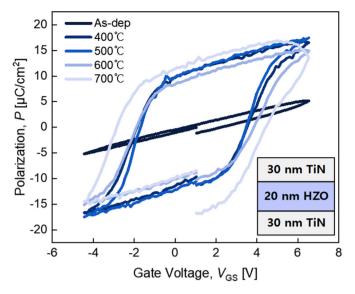

Fig. 2. Ferroelectric hysteresis loops of TiN/HZO/TiN capacitor with an HZO thickness of 20 nm annealed at various temperatures.

contamination sources [22]. EBL was carried out for gate patterning, and Ni/Au (50/50 nm) gate metal was formed via electron beam evaporation and lift-off process. The device was suitably fabricated with each part of the  $\beta\text{-}\text{Ga}_2\text{O}_3$  flake and HZO layer. Their components and accurate locations were confirmed through the scanning transmission electron microscopy (STEM)-energy dispersive X-ray spectroscopy

(EDS) mapping images, as shown in Fig. 1 (c). To check the ferroelectricity of HZO, TiN/HZO/TiN (30/20/30 nm) metal-ferroelectric-metal capacitors at different annealing temperatures were fabricated and characterized. As the annealing temperature increases, the formation of the ferroelectric phase and the crystallinity of the HZO layer are enhanced, leading to an increase in remanent polarization ( $P_r$ ) and consequently improved electrical characteristics. These changes are reflected in the polarization–voltage (P–V) loop results shown in Fig. 2. The devices were annealed at 400–700 °C in a N<sub>2</sub> environment for 1 min by rapid thermal annealing, exhibiting clear ferroelectric P-V hysteresis loops. The HZO layers of the fabricated Fe-FinFETs and planar FeFETs were annealed at 500 °C, where a clear ferroelectric hysteresis loop appeared.

#### 3. Results and discussion

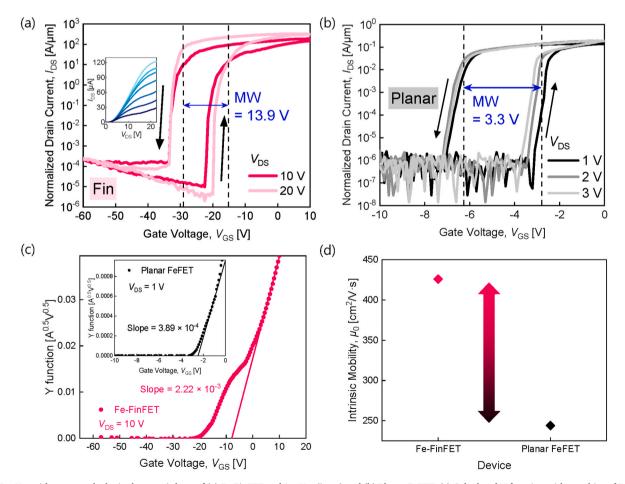

The drain-to-source current  $(I_{DS})$ -gate-to-source voltage  $(V_{GS})$  curves of Fe-FinFET and planar FeFET are shown in Fig. 3(a) and (b), which are considered normalized to the actual channel width for comparison of the intrinsic device properties.

The exfoliated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanomembrane flakes were obtained from the same bulk substrate, and flakes with a uniform thickness were selected and subjected to the same process to ensure device uniformity and comparability. A typical counter-clockwise loop with good polarization switching behavior was observed in the transfer characteristics, indicating reliable polarization switching. The key device performance parameters of Fe-FinFET are significantly superior to those of the planar FeFET. With the fin structure, these characteristics can be improved through enhanced gate controllability of the surrounding gate

Fig. 3.  $I_{DS}$ - $V_{GS}$  with counter-clockwise hysteresis loop of (a) Fe-FinFET and  $I_{DS}$ - $V_{DS}$  (inset) and (b) Planar FeFET. (c) Calculated Y-function with gate bias of Fe-FinFET and planar FeFET (inset). (d) Comparison of extracted intrinsic mobility using the Y-function method.

**Table 1**Comparison of electrical performances of fin and planar structures.

|                                 | Fe-FinFET           | Planar FeFET        |

|---------------------------------|---------------------|---------------------|

| I <sub>ON</sub> [A/μm]          | 16.93               | $3\times 10^{-3}$   |

| $I_{\rm ON}/I_{\rm OFF}$ ratio  | $2.3 \times 10^{7}$ | $8.1 \times 10^{4}$ |

| Subthreshold swing, SS [mV/dec] | 110                 | 160                 |

| Memory Window, MW [V]           | 13.9                | 3.3                 |

architecture and the strengthened electric field across the HZO layer, as demonstrated by the subsequent TCAD simulation. The wide  $V_{\rm GS}$  operation range reinforced by structural modifications is further extended through the incorporation of the UWBG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, ultimately leading to maximized memory window expansion. Indeed, the Fe-FinFET exhibited a MW of 13.9 V at the maximum sweep voltage from -60 V to 10 V on the HZO single layer, which is more than 4.2 times larger than that of planar FeFET at 3.3 V in the linear region, where the MW was extracted from the threshold voltage  $(V_T)$  difference. A wide MW is required to separate program and erase operations for discrete data storage in practical non-volatile memory applications [19,20]. Moreover, by achieving large MW, the ferroelectric memory can accurately implement multi-level memory states as a neuromorphic device. This multi-state storage capability enables precise modulation of synaptic weight values in neuromorphic computing, contributing to high recognition accuracy and energy-efficient operation [17,23,24]. In this way, the MW of 13.9 V demonstrates that the HZO/β-Ga<sub>2</sub>O<sub>3</sub> Fe-FinFET can be a strong candidate for future robust neuromorphic devices. The intrinsic.

mobility( $\mu_0$ ) is extracted using the Y-function method to analyze the impact of structural variation [25]. The Y-function is defined as  $Y = \frac{I_{DS}}{\sqrt{a_-}}$ ,

where  $g_m$  is transconductance. After obtaining the Y-function (shown in Fig. 3 (c)),  $\mu_0$  can be calculated using the slope obtained from the Y-function with  $C_{ox}$  and device geometry. The  $\mu_0$  of the Fe-FinFET is  $4.25 \times 10^2 \text{ cm}^2/\text{V} \cdot \text{s}$ , which is about 1.74 times improved compared to the planar FeFET, shown in Fig. 3 (d).

Table 1 presents a comparison of the properties of the  $HZO/\beta$ -Ga<sub>2</sub>O<sub>3</sub> Fe-FinFET with planar FeFET. Compared with the planar FeFET, the Fe-FinFET in this study exhibited enhanced electrical performances and excellent memory characteristics under high density.

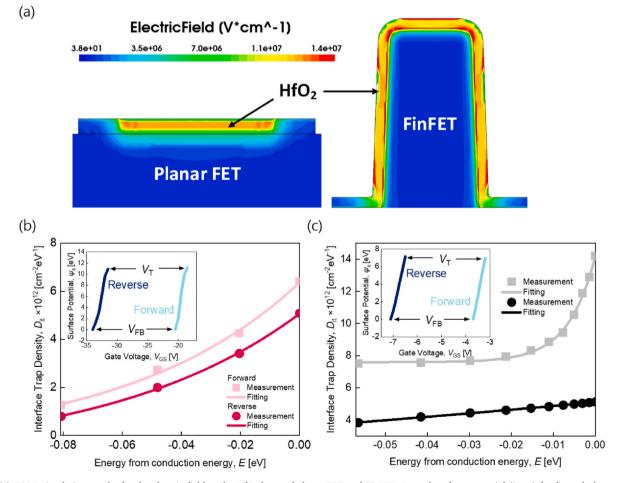

For the ferroelectric material to fully polarize, a sufficient electric field across the ferroelectric layer is necessary [26]. The electric field enhancement in the conventional FinFET of Si substrate and HfO<sub>2</sub> gate insulator was understood using technology computer-aided design (TCAD) simulation (Synopsys Sentaurus) [27]. The simulation condition was  $V_G = 5$  V,  $V_D = 0$  V,  $V_S = 0$  V, and HfO<sub>2</sub> layer thickness = 2 nm. As depicted in Fig. 4 (a), the FinFET has a higher electric field across the HfO<sub>2</sub> layer than the planar-structured FET; it is confirmed that as the electric field strength increases due to the increase of capacitance density and multidirectional potential gradients inherent in three-dimensional gate structure, polarization switching in HZO films becomes more complete and faster, indicating accelerated domain wall motion and enhanced dipole alignment under stronger fields [28–30].

The surface potential  $(\psi_S)$  and  $D_{it}$  were extracted using the differential body factor (DBT) technique for Fe-FinFETs and planar FeFETs, and the influence of internal field strength on interface trap behavior was investigated. These results are shown in Fig. 4(b) and (c), respectively [31,32]. The high agreement between the extracted results and the general  $D_{it}$  model indicates that the experimentally obtained results

Fig. 4. (a) TCAD simulation results for the electric field at the  $HfO_2$  layer of planar FET and FinFET.  $D_{it}$  and surface potential (inset) for fin and planar structure, shown in (b) and (c), respectively.

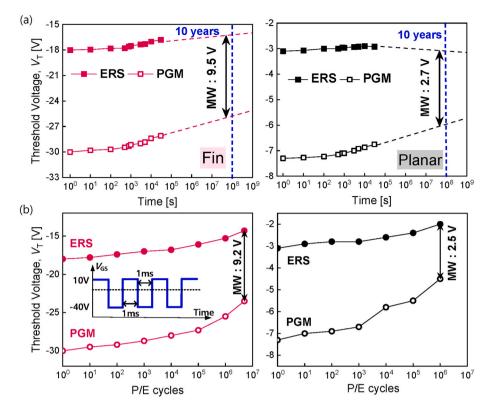

Fig. 5. (a) Retention and (b) Endurance characteristics of Fe-FinFET and planar FeFET, respectively.

from DBT from raw data fit the empirical model well, as a superposition of two exponential functions. The Fe-FinFET exhibits a larger  $\psi_S$  value within the same voltage range, indicating that the HZO is subjected to a higher electric field and possesses better switching characteristics. Under reverse bias (+ $\rightarrow$ -), the extracted  $D_{it}$  exhibited nearly identical trap levels in both devices, which is attributed to polarization-induced electron repulsion that suppresses carrier capture into the trap states. In contrast, under.

forward bias  $(-\to +)$ , the Fe-FinFET exhibited a  $D_{it}$  of  $6.4 \times 10^{12}$  cm $^{-2}$ eV $^{-1}$ , whereas the planar FeFET with a weaker electric field showed a higher  $D_{it}$  of  $1.4 \times 10^{13}$  cm $^{-2}$ eV $^{-1}$ . This can be explained by the relatively weaker polarization, which increases electron injection near the interface and thereby promotes trapping [33,34]. On the other side, in the Fe-FinFET with a strong electric field, the enhanced polarization switching induces more effective carrier displacement and recombination [4,35]. Therefore, the Fe-FinFET, indicating higher electric fields, exhibits enhanced ferroelectric polarization switching and lower  $D_{it}$ .

Retention and endurance characteristics to investigate the ferroelectric memory reliability of the  $\rm HZO/\beta\text{-}Ga_2O_3$  Fe-FinFET are shown in Fig. 5. According to the retention characteristics, when linearly extrapolated to 10 years, the MW of the Fe-FinFET is maintained over 9.5 V. The endurance performance as a memory device was tested by program/erase (PGM/ERS) cycling with a fixed pulse width of 1 ms and repeated voltages of -40 V and 10 V. The Fe-FinFET shows lower deterioration over up to  $10^6$  cycles at larger MW, compared to the planar FeFET. This demonstrates that the FinFET with its tri-gate structure enhances gate-to-channel coupling and electric field concentration, thereby stabilizing ferroelectric polarization and enabling efficient repeated switching.

The learning method was applied to the Canadian Institute for Advanced Research (CIFAR)-10 dataset containing RGB color images to the ResNet18 model as a Convolutional Neural Network (CNN) architecture for evaluation of recognition accuracy [36,37]. The ResNet18 architecture utilizes 17 convolutional layers that perform convolution

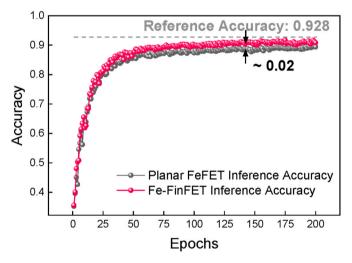

**Fig. 6.** CIFAR-10 accuracy using neural network simulation is performed using 7-bit synaptic weights for Fe-FinFET and 5-bit synaptic weights for planar FeFET.

operations and 10 output neurons to implement one fully connected layer. The simulation was implemented using TensorFlow by adjusting the resolution bits of each synaptic weight and neuron within the neural network, enabling inference [38,39].

Fig. 6 illustrates the validation accuracy during training when the resolution bits of Fe-FinFET and planar FeFET are implemented with the ResNet18 architecture. The validation dataset is sourced from the test dataset to evaluate the neural network's inference accuracy. The resolutions of the Fe-FinFET and planar FeFET devices in terms of synaptic weights in the neural network were measured at 7 bits and 5 bits, respectively, through our experimental programming measurements. By applying voltage pulses and calculating the number of stable and

distinguishable conductivity states, we confirm that Fe-FinFET and planar FeFET exhibited analog weight resolutions of 7 bits (128 states) and 5 bits (32 states), respectively. The inference accuracy of ResNet18, shown as the gray baseline in Fig. 6, is 92.8 %, with both synaptic weights and neurons represented in floating-point resolution [37]. The neural network performance with the Fe-FinFET device achieved an accuracy of 91.7 %, while that of the planar FeFET was 89.7 %. This suggests that Fe-FinFETs enable finer weight granularity, resulting in more precise updates and consistently higher accuracy across pulse epochs. Higher accuracy of Fe-FinFET-based neural networks reflects the device's capability to support reliable synaptic updates, which is advantageous for implementing biologically plausible learning rules and achieving high-performance neuromorphic computing systems.

#### 4. Conclusion

This study presented the first HZO/β-Ga<sub>2</sub>O<sub>3</sub> Fe-FinFET with a fin width of 100 nm. We report that the UWBG Fe-FinFETs achieved low SS of 110 mV/dec, high Ion/Ioff ratio of  $2.3 \times 10^7$ , and notably a wide MW of 13.9 V in a single ferroelectric layer, which was validated through simulations and Dit compared to planar FeFETs. In addition, highly reliable retention and endurance characteristics are confirmed by electrical measurements, and high accuracy is achieved through CIFAR-10 simulation, confirming high reliability for device operation. Notably, this study demonstrated that the integration of HZO/UWBG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with the FinFET architecture enabled high-performance and reliable ferroelectric memory operation, highlighting its potential for implementing high-performance synaptic memory applications. In this study, the relatively high operation voltage and modest switching speed reflect limits in VT control and interfacial/ferroelectric switching kinetics. To address these limitations, comprehensive device- and process-level cooptimization—spanning the gate stack, ferroelectric/semiconductor thicknesses, interface quality, and operating schemes—will be required within the scaled device architecture, and further study is needed.

This work was supported by the Nano & Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (No. RS-2024-00460372), in part by the Nano-Material Technology Development Program (2009-0082580) through the National Research Foundation (NRF) of Korea funded by the Ministry of Science, in part by the Technology Innovation Program (RS-2025-25454815) funded by the Ministry of Trade Industry & Energy (MOTIE, Korea), in part by the Institute of Information & Communications Technology Planning & Evaluation (IITP)-Innovative Human Resource Development for Local Intellectualization program grant funded by the Korea government (MSIT) (IITP-2025-RS-2024-00439292), in part by the Korea Basic Science Institute (National research Facilities and Equipment Center) grant funded by the Ministry of Education (grant No. RS-2024-00436672), in part by Industry-Academia-Research Collaboration R&D Project funded by the Ministry of SMEs and Startups (No. RS-2025-02318173), and in part by the Regional Innovation System & Education (RISE) initiative funded by the Ministry of Education and administered by the National Research Foundation of Korea (NRF). The EDA tool was also supported in part by the IC Design Education Center (IDEC).

#### CRediT authorship contribution statement

Seohyeon Park: Writing – review & editing, Writing – original draft, Visualization, Validation, Supervision, Resources, Project administration, Methodology, Investigation, Formal analysis, Data curation, Conceptualization. Jaewook Yoo: Writing – review & editing, Formal analysis, Data curation, Conceptualization. Seokjin Oh: Validation, Software. Hongseung Lee: Software. Minah Park: Investigation. Seongbin Lim: Investigation. Soyeon Kim: Visualization. Sojin Jung: Visualization. Bongjoong Kim: Resources. Keun Heo: Resources. Taehwan Moon: Methodology, Formal analysis, Conceptualization.

TaeWan Kim: Resources. Mengwei Si: Resources, Data curation. Peide D. Ye: Resources. Hagyoul Bae: Supervision, Conceptualization.

#### **Declaration of competing interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Data availability

Data will be made available on request.

#### References

- [1] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, S. Yamakoshi, Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates, Appl. Phys. Lett. 100 (1) (2012) 013504, https://doi.org/10.1063/1.3674287.

- [2] H. Bae, S.G. Nam, T. Moon, Y. Lee, S. Jo, D.-H. Choe, S. Kim, K.-H. Lee, J. Heo, Subns polarization switching in 25nm FE FinFET toward post CPU and spatial-energetic mapping of traps for enhanced endurance, IEDM Tech. Dig (2020), https://doi.org/10.1109/IEDM13553.2020.9372076, 31.3.1–31.3.4.

- [3] W.S. Hwang, A. Verma, H. Peelaers, V. Protasenko, S. Rouvimov, H. Xing, A. Seabaugh, W. Haensch, C. Van de Walle, Z. Galazka, M. Albrecht, R. Fornari, D. Jena, High-voltage field effect transistors with wide-bandgap β-Ga<sub>2</sub>O<sub>3</sub> nanomembranes, Appl. Phys. Lett. 104 (20) (2014) 203111, https://doi.org/ 10.1063/1.4879800.

- [4] M.H. Wong, K. Sasaki, A. Kuramata, S. Tamakoshi, M. Higashiwaki, Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V, IEEE Electron Device Lett. 37 (2) (2016) 212–215, https://doi.org/10.1109/LED.2015.2512279.

- [5] M. Higashiwaki, K. Sasaki, T. Kamimura, M.H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui, S. Yamakoshi, Depletion-mode Ga2O3 metal-oxidesemiconductor field-effect transistors on β-Ga2O3 (010) substrates and temperature dependence of their device characteristics, Appl. Phys. Lett. 103 (12) (2013) 123511, https://doi.org/10.1063/1.4821858.

- [6] M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, S. Yamakoshi, Recent progress in Ga<sub>2</sub>O<sub>3</sub> power devices, Semicond. Sci. Technol. 31 (3) (2016) 034001, https://doi.org/10.1088/0268-1242/31/3/ 034001.

- [7] M. Baldini, Z. Galazka, G. Wagner, Recent progress in the growth of β-Ga<sub>2</sub>O<sub>3</sub> for power electronics applications, Mater. Sci. Semicond. Process. 78 (2018) 132–146, https://doi.org/10.1016/j.mssp.2017.10.04.

- [8] H. Bae, T.J. Park, J. Noh, W. Chung, M. Si, S. Ramanathan, P.D. Ye, First demonstration of robust tri-gate β-Ga<sub>2</sub>O<sub>3</sub> nano-membrane field-effect transistors, Nanotechnology 33 (12) (2021) 125201, https://doi.org/10.1088/1361-6528/ ac3611

- [9] T.S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, U. Böttger, Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors, IEDM Tech. Dig (2011) 24.5.1–24.5.4, https://doi.org/10.1109/IEDM.2011.6131606.

- [10] A.E. Islam, N.P. Sepelak, K.J. Liddy, R. Kahler, J. Williams, D.M. Dryden, A. J. Green, K.D. Chabak, High temperature operation of β-Ga<sub>2</sub>O<sub>3</sub> transistors, Proc. Int. Symp. Microelectronics (IMAPS) (2021) 288–293, https://doi.org/10.4071/2380-4505-2021.1.000288.

- [11] J.Y. Tsao, S. Chowdhury, M.A. Hollis, D. Jena, N.M. Johnson, K.A. Jones, R. J. Kaplar, S. Rajan, C.G. Van de Walle, E. Bellotti, C.L. Chua, R. Collazo, M. E. Coltrin, J.A. Cooper, K.R. Evans, S. Graham, T.A. Grotjohn, E.R. Heller, M. Higashiwaki, M.S. Islam, P.W. Juodawlkis, M.A. Khan, A.D. Koehler, J.H. Leach, U.K. Mishra, R.J. Nemanich, R.C.N. Pilawa-Podgurski, J.B. Shealy, Z. Sitar, M. J. Tadjer, A.F. Witulski, M. Wraback, J.A. Simmons, Ultrawide-bandgap semiconductors: research opportunities and challenges, Adv. Electron. Mater. 4 (1) (2018) 1600501, https://doi.org/10.1002/aelm.201600501.

- [12] X. Lyu, M. Si, X. Sun, M.A. Capano, H. Wang, P.D. Ye, Ferroelectric and antiferroelectric hafnium zirconium oxide: scaling limit, switching speed and record high polarization density, IEEE Symp. VLSI Technol. T4–4 (2019) T44–T45, https://doi.org/10.23919/VLSIT.2019.8776548.

- [13] J. Müller, T.S. Bösckee, S. Müller, E. Yurchuka, P. Polakowski, J. Paul, D. Martin, T. Schenk, K. Khullar, A. Kersch, W. Weinreich, S. Riedel, K. Seidel, A. Kumar, T. M. Arruda, S.V. Kalinin, T. Schlösser, R. Boschke, R. van Bentum, U. Schröder, T. Mikolajick, Ferroelectric hafnium oxide: a CMOS-compatible and highly scalable approach to future ferroelectric memories, IEDM Tech. Dig (2013) 10.8.1–10.8.4, https://doi.org/10.1109/IEDM.2013.6724605.

- [14] W. Chung, M. Si, P.R. Shrestha, J.P. Campbell, K.P. Cheung, P.D. Ye, First direct experimental studies of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric polarization switching Down to 100-picosecond in Sub-60mV/dec germanium ferroelectric nanowire FETs, IEEE Symp. VLSI Technol. (2018) 89–90, https://doi.org/10.1109/VLSIT.2018.8510652.

- [15] M. Seo, M.-H. Kang, S.-B. Jeon, H. Bae, J. Hur, B.C. Jang, S. Yun, S. Cho, W.-K. Kim, M.-S. Kim, K.-M. Hwang, S. Hong, S.-Y. Choi, Y.-K. Choi, First demonstration of a logic-process compatible Junctionless ferroelectric FinFET synapse for neuromorphic applications, IEEE Electron Device Lett. 39 (9) (2018) 1445–1448, https://doi.org/10.1109/LED.2018.2852698.

- [16] J. Yoo, H. Song, H. Lee, S. Lim, S. Kim, K. Heo, H. Bae, Recent research for HZO-based ferroelectric memory towards In-Memory computing applications, Electronics 12 (10) (2023) 2297, https://doi.org/10.3390/electronics12102297.

- [17] J. Noh, H. Bae, J. Li, Y. Luo, Y. Qu, T.J. Park, M. Si, X. Chen, A.R. Charnas, W. Chung, X. Peng, S. Ramanathan, S. Yu, P.D. Ye, First experimental demonstration of robust HZO/β-Ga<sub>2</sub>O<sub>3</sub> ferroelectric field-effect transistors as synaptic devices for artificial intelligence applications in a high-temperature environment, IEEE Trans. Electron. Dev. 68 (5) (2021) 2515–2521, https://doi.org/10.1109/TED.2021.3064783.

- [18] R. Mitdank, S. Dusari, C. Bülow, M. Albrecht, Z. Galazka, S.F. Fischer, Temperature-dependent electrical characterization of exfoliated β-Ga<sub>2</sub>O<sub>3</sub> micro flakes, Phys. Status Solidi 211 (3) (2014) 543–549, https://doi.org/10.1002/ pssa.201330671.

- [19] M.H. Park, Y.H. Lee, T. Mikolajick, U. Schröeder, C.S. Hwang, Review and perspective on ferroelectric HfO2-based thin films for memory applications, MRS Commun. 8 (3) (2018) 795–808, https://doi.org/10.1557/mrc.2018.175.

- [20] H. Mulaosmanovic, E.T. Breyer, T. Mikolajick, S. Slesazeck, Ferroelectric FETs with 20-nm-Thick HfO<sub>2</sub> layer for large memory window and high performance, IEEE Trans. Electron. Dev. 66 (9) (2019) 3828–3833, https://doi.org/10.1109/ TFD 2019 2930749

- [21] H. Bae, J. Noh, S. Alghamdi, M. Si, P.D. Ye, Ultraviolet light-based current–voltage methosd for simultaneous extraction of Donor- and acceptor-like interface traps in β-Ga<sub>2</sub>O<sub>3</sub> FETs, IEEE Electron Device Lett. 39 (11) (2018) 1708–1711, https://doi. org/10.1109/IFD.2018.2871801.

- [22] M. Si, L. Yang, H. Zhou, P.D. Ye,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanomembrane negative capacitance field-effect transistors with steep subthreshold slope for wide band gap logic applications, ACS Omega 2 (10) (2017) 7136–7140, https://doi.org/10.102c1/acsomega.7b01289.

- [23] H. Xiang, Y.-C. Chien, L. Li, H. Zheng, S. Li, N.T. Duong, Y. Shi, K.-W. Ang, Enhancing memory window efficiency of ferroelectric transistor for neuromorphic computing via two-dimensional materials integration, Adv. Funct. Mater. 33 (42) (2023) 2304657, https://doi.org/10.1002/adfm.202304657.

- [24] G.S. Lee, J.-S. Jeong, M.K. Yang, J.D. Song, Y.T. Lee, H. Ju, Non-volatile memory behavior of interfacial InO<sub>x</sub> layer in InAs nano-wire field-effect transistor for neuromorphic application, Appl. Surf. Sci. 541 (2021) 148483, https://doi.org/ 10.1016/j.apsusc.2020.148483.

- [25] G. Ghibaudo, New method for the extraction of MOSFET parameters, Electron. Lett. 24 (9) (1988) 543, https://doi.org/10.1049/el:19880369.

- [26] K. Lee, J.-H. Bae, S. Kim, J.-H. Lee, B.-G. Park, D. Kwon, Ferroelectric-gate field-effect transistor memory with recessed channel, IEEE Electron Device Lett. 41 (8) (2020) 1201–1204, https://doi.org/10.1109/LED.2020.3001129.

- [27] R. Tiwari, N. Parihar, K. Thakor, H.Y. Wong, S. Motzny, M. Choi, V. Moroz, S. Mahapatra, A 3-D TCAD framework for NBTI—Part I: implementation details and FinFET channel material impact, IEEE Trans. Electron. Dev. 66 (5) (2019) 2086–2092, https://doi.org/10.1109/TED.2019.2906339.

- [28] S.-C. Yan, G.-M. L-n, C.-J. Sun, Y.-H. Chen, C.-H. Wu, H.-K. Peng, Y.-H. Lin, Y.-H. Wu, Y.-C. Wu, High speed and large memory window ferroelectric HfZrO<sub>2</sub> FinFET for high-density nonvolatile memory, IEEE Electron Device Lett. 42 (9) (2021) 1307–1310, https://doi.org/10.1109/LED.2021.3097777.

- [29] E. Kondratyuk, A. Chouprik, Polarization switching kinetics in thin ferroelectric HZO films, Nanomaterials 12 (23) (2022) 4126, https://doi.org/10.3390/ nano12234126

- [30] C. Alessandri, P. Pandey, A. Abusleme, A. Seabaugh, Switching dynamics of ferroelectric Zr-Doped HfO<sub>2</sub>, IEEE Electron Device Lett. 39 (11) (2018) 1780–1783, https://doi.org/10.1109/LED.2018.2872124.

- [31] D. Yun, M. Bae, J. Jang, H. Bae, J.S. Shin, E. Hong, J. Lee, D.H. Kim, D.M. Kim, Differential body-factor technique for characterization of interface traps in MOSFETs, IEEE Electron Device Lett. 32 (9) (2011) 1206–1208, https://doi.org/10.1109/LED.2011.2160709.

- [32] S. Park, J. Yoo, M. Park, H. Lee, H. Song, S. Lim, S. Kim, S. Jung, T.W. Kim, Y.-K. Choi, H. Bae, Determination of donor- and acceptor-like interface trap density using photoresponsive GIDL in vertically stacked Si-NW GAA FETs, Appl. Phys. Lett. 126 (12) (2025) 122102, https://doi.org/10.1063/5.0254522.

- [33] J.Y. Park, D.-H. Choe, D.H. Lee, G.T. Yu, S.H. Kim, G.H. Park, S.-G. Nam, H.J. Lee, S. Jo, B.J. Kuh, D. Ha, Y. Kim, J. Heo, M.H. Park, Revival of ferroelectric memories based on emerging fluorite-structured ferroelectrics, Adv. Mater. 35 (43) (2023) 2204904, https://doi.org/10.1002/adma.202204904.

- [34] W. Shin, C.-H. Han, J. Kim, R.-H. Koo, K.K. Min, D. Kwon, Effects of charge imbalance on field-induced instability of Hf02-Based ferroelectric tunnel junctions, Adv. Electron. Mater. 11 (2) (2025) 2400299, https://doi.org/10.1002/ aelm.202400299.

- [35] S.-C. Yan, C.-H. Wu, C.-J. Sun, Y.-W. Lin, Y.-J. Yao, Y.-C. Wu, Trench FinFET nanostructure with advanced ferroelectric nanomaterial HfZrO2 for Sub-60-mV/Decade subthreshold slope for low power application, Nanomaterials 12 (13) (2022) 2165, https://doi.org/10.3390/nano12132165.

- [36] A. Krizhevsky, V. Nair, G. Hinton, CIFAR-10 and CIFAR-100 datasets. https://www.cs.toronto.edu/~kriz/cifar.html. (Accessed 1 May 2019).

- [37] S. Targ, D. Almeida, K. Lyman, Resnet in resnet: generalizing residual architectures, CoRR (2016) 08029 abs/1603.

- [38] T. Bannink, A. Hillier, L. Geiger, T. de Bruin, L. Overweel, J. Neeven, K. Helwegen, Larq compute engine: design, benchmark and deploy state-of-the-art binarized neural networks, Proc. Mach. Learn. Syst. 3 (2021) 680–695.

- [39] M. Abadi, P. Barham, J. Chen, Z. Chen, A. Davis, J. Dean, M. Devin, S. Ghemawat, G. Irving, M. Isard, M. Kudlur, J. Levenberg, R. Monga, S. Moore, D.G. Murray, B. Steiner, P. Tucker, V. Vasudevan, P. Warden, M. Wicke, Y. Yu, X. Zheng, TensorFlow: a system for large-scale machine learning, in: Proceedings of the 12th USENIX Symposium on Operating Systems Design and Implementation (OSDI '16), 2016, pp. 265–283.