# Impact of Channel Material, Interface Quality, and Polarization on Memory Window of Interfacial Layer-Free FeFET With Oxide Semiconductor

Zikang Yao<sup>©</sup>, Danyang Chen, *Graduate Student Member, IEEE*, Tianning Cui<sup>®</sup>, *Graduate Student Member, IEEE*, Yulong Dong, Zhiyu Lin, Graduate Student Member, IEEE, Jingguan Liu<sup>10</sup>, Member, IEEE, Mengwei Si<sup>®</sup>, Member, IEEE, and Xiuyan Li<sup>®</sup>, Member, IEEE

Abstract—This study systematically investigates the modulation of the memory window (MW) in interfacial layer (IL)-free and  $Hf_xZr_{1-x}O_2$  (HZO)-based ferroelectric field-effect transistors (FeFETs) with oxide channel by engineering oxide semiconductor materials, annealing processes, and polarization in HZO. Our findings reveal that the MW in such an FeFET is predominantly governed by the positive charge supply capability of the semiconductor layer and the interface properties between the ferroelectric (FE) layer and the semiconductor. Specifically, higher doping concentrations in the channel material and less interface trapping are shown to enhance the MW. In contrast, polarization shows limited effect. These results provide critical insights into the underlying mechanisms of MW optimization in FeFETs with oxide semiconductor channels.

Index Terms—FE field-effect transistor (FeFET), Ferroelectric  $Hf_xZr_{1-x}O_2$  (Fe-HZO), metal FE semiconductor (MFS) structure, oxide semiconductor.

# I. Introduction

ZO-BASED ferroelectric field-effect transistors (FeFETs) with oxide semiconductor channel (OS)-FeFET, such as In<sub>2</sub>O<sub>3</sub> (InO), ZnO, and indium-gallium-zinc oxide (IGZO), have garnered significant attention in recent years due to their promising potential for achieving superior endurance performance and compatibility with monolithic

Received 21 April 2025; revised 20 June 2025 and 7 July 2025; accepted 9 July 2025. Date of publication 25 July 2025; date of current version 25 August 2025. This work was supported by the National Natural Science Foundation of China under Grant 62274109, Grant 6245003, and Grant 52350195. The review of this article was arranged by Editor F. M. Puglisi. (Corresponding authors: Mengwei Si; Xiuyan Li.)

Zikang Yao, Danyang Chen, Tianning Cui, Yulong Dong, Jingquan Liu, and Xiuyan Li are with the National Key Laboratory of Advanced Micro and Nano Manufacture Technology, Shanghai Jiao Tong University, Shanghai 200240, China (e-mail: xiuyanli@situ.edu.cn).

Zhiyu Lin and Mengwei Si are with School of Integrated Circuits and the School of Information Science and Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China (e-mail: mengwei.si@situ.edu.cn).

Digital Object Identifier 10.1109/TED.2025.3589546

3-D integration [1], [2], [3], [4]. Compared with conventional Si-FeFETs, which require an interfacial layer (IL) between Si and FE layer [5], [6], [7], [8], [9], OS-FeFETs may enable IL-free operation owing to the inherent compatibility of oxide-oxide interfaces, thereby eliminating charge trapping-induced endurance degradation from subnanometer ILs [10], [11], [12], [13], [14], [15]. This is promising to solve the problem of interface degradation in endurance cycling and to improve endurance performance which is the key limit for Si-FeFET. Up to date, HZO-based OS-FeFETs with remarkable endurance exceeding 10<sup>9</sup> cycles [16], [17] and feasibility for 3-D integration [18], [19] have been demonstrated. For example, Chen et al. [17] achieved  $>10^{10}$ endurance by optimizing the FE/OS interface, scaling IGZO thickness, and designing a dual-composition channel, with a memory window (MW) >1 V on 300-mm wafers. Feng et al. [18] reported the first 3-D vertical FE NOR memory with back-end-of-line (BEOL)-compatible processing, featuring a novel side-fin structure that achieved  $>10^6$  ON/OFF ratio and 4-V MW. Lin et al. [19] demonstrated 3-D vertical all-oxide transistors using thick degenerated atomic layer deposition (ALD) InO as both gate electrode and source/drain contacts, achieving >10<sup>5</sup> ON/OFF ratio, and robust endurance (>10<sup>12</sup> cycles) in FeFET configuration with 1.85-V MW. However, these properties were obtained in OS-FeFET structures with an IL or with metal capping during HZO crystallization and removing the metal after that. Satisfying properties have rarely been demonstrated in a real IL-free FeFET due to severely limited MW [20].

These issues have been more or less discussed in literatures about OS-FeFET reported so far. For example, Si et al. [21] have pointed out the necessity of IL for getting enough MW in both the OS-FeFETs and Si-FeFETs by physically modeling of charge balance [22]. Tian et al. [13] improved the stability of MW by introducing nitrogen-incorporated SiON IL and regulating Hf:Zr ratio with near-zero MW

loss. Mo et al. [2] demonstrated that 3-D nanowire FeFETs achieve the large MW due to electric field concentration via Gauss's law, while reducing channel length, diameter, and IGZO thickness enhances MW by strengthening electrostatic coupling and voltage division effects. Yoo et al. [23] achieved a record-high MW of 17.8 V in IGZO FeFETs by introducing an oxygen-deficient intermediate channel and a gate interlayer, enabling full-loop polarization switching. In some papers, MW modulation has also been achieved through engineering device architectures and inducing antiferroelectric (AFE) layer. Mo et al. [24] simulated a double-gate IL-free IGZO-FeFET with controllable MW by fixing the body potential using the top gate. Wang et al. [25] achieved precise tuning of MW from clockwise hysteresis to over beyond twice the coercive voltage in FeFETs with an internal floating gate through controlled scaling of area ratio. Our previous work demonstrated that IL-free FeFETs with IGZO fail to achieve MW due to insufficient positive charge compensation and this issue could be solved by replacing FE-HZO with AFE-HZO [20]. Therefore, key issues arise as follows: 1) what are the intrinsic physics determining the MW in OS-FeFET and 2) how the MW in an OS-FeFET could have been engineered.

Despite the many experimental modulation of MW in FeFET by incorporating IL or engineering structure, a comprehensive understanding of above key issue remains unclear: how do various factors including channel material, quality of interface between the FE layer and channel, and polarization in FE layer intrinsically affect the MW of OS-FeFET? This issue is particularly pronounced in OS-FeFET characterized by an inherent scarcity of holes in the channel, which critically disrupts charge compensation for polarization switching in FE layer. To study this issue, using the real IL-free OS-FeFET structures simply, this work presents a comprehensive experimental and theoretical investigation into MW modulation by different channel materials (InO, ZnO, IGZO), annealing processes and passivation layer on channel. Our findings provide new insights into the interplay between the positive charge supply capability of the channel, charge trapping/detrapping at the interface between the FE layer and channel, and the remanent polarization  $(P_r)$  of HZO, revealing mechanisms that dictate MW behavior. This study advances the understanding of MW control in HZO-based FeFETs and offers guidance for optimizing device performance in future memory applications.

# II. EXPERIMENT

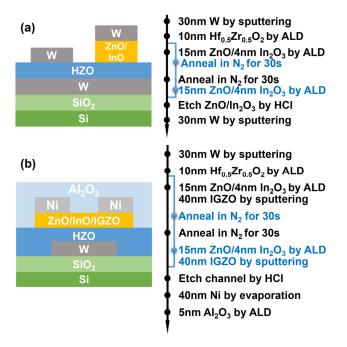

Fig. 1. illustrates the fabrication process and structural configuration of FE capacitors and OS-FeFETs. The process begins with the deposition of a 30-nm tungsten (W) layer via magnetron sputtering on a SiO<sub>2</sub>/Si substrate, serving as the bottom/gate electrode. Subsequently, a 10-nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin film is grown by thermal ALD at 250 °C, using tetrakis (dimethylamido) hafnium (TDMA-Hf) and tetrakis (dimethylamido) zirconium (TDMA-Zr) as metal precursors and deionized water (DIW) as the oxygen source. The semiconductor layer, either 15-nm ZnO or 5-nm InO, is deposited on the HZO layer via thermal ALD at 175 °C and 225 °C with

Fig. 1. Structure and process flow of (a) FE capacitors and (b) FeFET devices in the present work. Two kinds of semiconductor materials and two kinds of annealing processes were used.

diethylzinc (DEZn) and trimethylindium (TMIn) as metal precursors. While 40-nm IGZO layer is deposited by magnetron sputtering. Rapid thermal annealing (RTA) is performed either after HZO layer deposition (postdeposition annealing, PDA) or after OS layer deposition (postchannel annealing, PCA) at 450 °C $\sim$ 550 °C for 30 s in a nitrogen (N<sub>2</sub>) atmosphere. For FE-capacitor fabrication, the OS layers are selectively etched by dilute hydrochloric acid, followed by the deposition of a 30-nm W top electrode by magnetron sputtering. Notably, the etching rate of OS by HCl is much quicker than that of HZO because HZO was crystallized, and a selective etching could be obtained. For FeFET devices, source and drain electrodes are formed by thermal evaporation of 40-nm nickel (Ni). In addition, a subset of the transistors incorporate a 5-nm Al<sub>2</sub>O<sub>3</sub> passivation layer on the OS layer, which was deposited by thermal ALD at 100 °C using trimethylaluminum (TMA) as the aluminum precursor.

To investigate crystal phase of HZO films and enhance signal legibility, the X-ray diffraction (XRD) was used with grazing-incidence mode (GIXRD) [26]. The polarization–voltage (P-V) hysteresis loops of capacitors were characterized under a bipolar voltage sweep of  $\pm 3$  V with a frequency of 10 kHz. And the transfer characteristic curves of FeFETs were measured with a source–drain voltage  $(V_{\rm DS})$  of 0.1 V and a gate voltage  $(V_{\rm GS})$  of  $\pm 3$  V, sweeping in 50-mV steps by the semiconductor parameter analyzer (Keithley 4200).

### III. EXPERIMENTAL RESULTS

# A. Effect of Semiconductor and Annealing Process on Pr

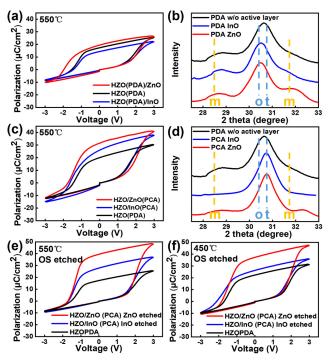

The effects of the OS material and annealing process on  $P_r$  of FE-HZO layer were first considered. Fig. 2 shows the P-V and GIXRD characteristics of HZO/OS capacitors in

Fig. 2. P-V loops and GIXRD results of HZO/InO and HZO/ZnO capacitors. (a) and (b) PDA and (c) and (d) PCA respectively. P-V loops under PCA temperature of (e) 550 °C and (f) 450 °C with channel materials removed before sputtering of top electrode.

both PDA and PCA cases. The results of samples without OS layer were also compared. In case of PDA, the P-V characteristics and crystalline structures of HZO/InO and HZO/ZnO samples are similar [Fig. 2(a) and (b)]. They are also similar to those of HZO sample without OS layer. This is understandable as the polarization is not affected by the process after PDA obviously. The slight difference in  $P_r$ may arise from the difference in voltage dropped on OS layer. In contrast, the P-V results of HZO/InO and HZO/ZnO capacitors with PCA demonstrate obvious difference [Fig. 2(c)].  $P_r$ of HZO/ZnO capacitors is larger than that of HZO/InO ones and both are larger than that of HZO capacitors with PDA. Meanwhile, GIXRD results show that the formation of the monoclinic-phase decrease is suppressed in HZO with PCA [Fig. 2(d)]. Note that the OS layer divides a part of voltage applied on HZO/OS capacitor, so that the voltage drop on HZO is not fair for comparing  $P_r$  value between HZO/InO and HZO/ZnO samples. To eliminate this effect, an additional set of capacitors were prepared by completely removing the OS layer via hydrochloric acid etching after the PCA process, followed by deposition of top electrodes. Interestingly, the HZO film with ZnO capping in PCA exhibited an obviously higher  $P_r$  than the film with InO capping [Fig. 2(e) and (f)]. And such a difference is larger with higher PCA temperature. This difference is considered to be likely attributed to different strain values induced by different OS layers during annealing [20], [27].

# B. Effect of OS Channel and Annealing Process on MW

Next, the MW characteristics of OS-FeFETs fabricated with different annealing processes and OS materials are

Fig. 3.  $I_{\rm DS}-V_{\rm GS}$  characteristics of FeFET for (a) InO with PDA, (b) InO with PCA, (c) ZnO with PDA, (d) ZnO with PCA, (e) IGZO with PDA, and (f) IGZO with PCA before passivation. Notably, the hysteresis loop in (c) exhibits a reversed directionality, as explicitly indicated in the legend.

systematically investigated. The  $I_{\rm DS}-V_{\rm GS}$  characteristics of samples with three kinds of OS material and with both PDA and PCA are illustrated in Fig. 3. All the FeFETs with InO-and ZnO-channel demonstrate pronounced counterclockwise hysteresis during the first cycle of voltage sweeping. However, the MW is reduced in subsequent cycles rapidly. Interestingly, an obvious MW is always maintained in InO-FeFET with both PDA and PCA process as well as in ZnO-FeFET with PCA, while it disappears in ZnO-FeFET with PDA where the hysteresis loop transitions from counterclockwise to clockwise after the first sweep cycle. Furthermore, IGZO-FeFETs exhibit no detectable counterclockwise hysteresis observed throughout multiple measurement cycles.

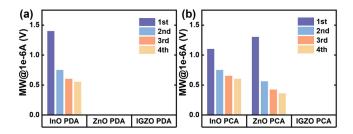

It has been proposed that the large MW in the first cycle may result from polarization changing in the initial defect/domain reconfiguration [28], [29], [30]. Therefore, the stabilized MW values after the first cycle should be considered for more accurate comparison and analysis quantitatively. Fig. 4 summarizes the MWs extracted at a drain current of  $1 \times 10^{-6}$ A in the first to forth sweeping cycles for three kinds of OS-FeFETs with PDA and PCA. Interestingly, the annealing process shows a critical effect on MW. OS-FeFETs with the PCA process exhibit a larger MW compared with those with PDA in both InO and ZnO cases. Since both ZnO- and IGZO-FeFETs with PDA show clockwise hysteresis in the  $I_{\rm DS}-V_{\rm GS}$  characteristics which is probably due to interface charge trapping [31], we consider that the PCA process improves the interface quality between the FE layer and OS channel by suppressing interface traps. In addition, under the same annealing process, InO FeFETs demonstrate a larger MW compared with ZnO devices, despite the fact that  $P_r$  in

Fig. 4. MW of FeFET for (a) PDA and (b) PCA annealing process in the first four  $I_{\rm DS}-V_{\rm GS}$  tests before passivation.

HZO/ZnO capacitor with PCA is significantly higher than that in InO one. These results clearly demonstrate that both OS material and annealing process are significant for controlling MW in FeFET rather than  $P_{\rm r}$  value in HZO layer.

#### C. Effect of Passivation Layer on MW

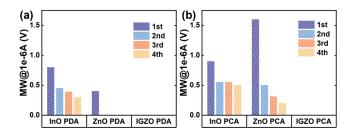

In addition, the effect of a 5-nm Al<sub>2</sub>O<sub>3</sub> passivation layer, which is deposited on the channel layers at 100 °C, on the  $I_{DS}-V_{GS}$  characteristics of these OS-FeFETs was also investigated. The relatively low deposition temperature here is to prevent the secondary annealing of the device during passivation, which may induce a drastic change in the oxygen vacancy concentration of the channel. Such a passivation layer has been generally used for protecting the device from ambient exposure [32], [33], [34], minimizing threshold voltage  $(V_{th})$ drift to ensure stable MW. Fig. 5 shows the  $I_{DS}$ - $V_{GS}$  curves of the above OS-FeFETs with passivation layer. Compared with aforementioned samples, it is observed that there is no obvious change in MW after deposition of Al<sub>2</sub>O<sub>3</sub>. The MWs extracted in the first to forth sweeping cycles are also summarized in Fig. 6. The impact of OS material and annealing process on MW keeps the same with that of devices without passivation. While all the absolute values of MW decreased slightly. This is maybe due to an effect of passivation layer on the positive charge supplying, as the channel layer is relatively thin. It is noteworthy that the IGZO PDA sample exhibits a normally OFF behavior in Figs. 3(e) and 5(e), whereas the IGZO PCA sample shows a negative threshold voltage as shown in Figs. 3(f) and 5(f). This phenomenon may be attributed to interfacial negative charges introduced during the sputtering process, which are subsequently eliminated by PCA through thermal remediation.

# IV. DISCUSSION

Finally, the issues why and how MW is controlled by OS material and interface quality rather than  $P_{\rm r}$  in FE layer are discussed. Theoretically, in an ideal FeFET with no defects at interface and/or in dielectric and with sufficient compensation charge in channel for full polarization switching, the MW is obtained [20], [22]

$$MW = 2P_r/C_{FE} \tag{1}$$

where  $P_r$  is the residual polarization and  $C_{FE}$  is the capacitance of FE layer of unit area. In this case, MW is mainly controlled by  $P_r$  with full polarization switching. In actual case, however,

Fig. 5.  $I_{\rm DS}-V_{\rm GS}$  characteristics of FeFET for (a) InO with PDA, (b) InO with PCA, (c) ZnO with PDA, (d) ZnO with PCA, (e) IGZO with PDA, and (f) IGZO with PCA after passivation. Notably, the hysteresis loop in (c) exhibits a reversed directionality, as explicitly indicated in the legend.

Fig. 6. MW of FeFET for (a) PDA and (b) PCA annealing process in the first four  $I_{\rm DS}-V_{\rm GS}$  tests after passivation.

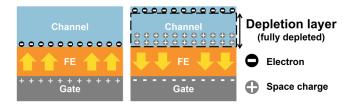

polarization switching needs both positive and negative compensation charges from channel or interface between the FE and channel layer. Thin OS film, however, can supply enough negative charge by free electrons but cannot do sufficient positive charges due to lack of free holes. Supplying of the positive space charges, generally originated from positively charged oxygen vacancies  $(V_0^{2+})$  as schematically shown in Fig. 7, needs a large potential drop on OS layer which involves negative feedback [35], [36]. Moreover, high quality of interface could also not supply enough positive charges. As a result, only limited domains determined by the total amount of positive charges from channel and interface can be switched, contributing to MW. Meanwhile, the charge trapping/detrapping at the defects in HZO, channel, or at the interface will induce a clockwise hysteresis. In some cases, mobile-ionic effect also results in counterclockwise hysteresis, affecting the actual MW estimation in experiments as reported [37], [38].

Here, for simplicity, we ignore the ionic effect and assume all the charge trapping/detrapping effects which induce

Fig. 7. Schematics of charge compensation in FeFET with oxide semiconductor. Sufficient free electrons can be supplied but positive charges are limited.

clockwise hysteresis as an effective effect at the interface. Then the actual MW' becomes

$$MW' = (\Delta P_{FE} - 2Q')/C_{FE}$$

(2)

where  $\Delta P_{\text{FE}}$  is actually switched polarization in HZO, Q' represents the effective trapping/detrapping charge at the interface, and factor 2 originates from the dual-sweep in transfer characteristic measurement. Since  $\Delta P_{\text{FE}}$  is determined by the positive compensation charges from interface ( $Q^*$ ) and from space charges in channel ( $Q_{\text{S}}$ ), it can be described as

$$Q^* + Q_S = Q^* + q N_D W_D = \Delta P_{FE}/2 + \epsilon_0 \epsilon_{FE} E_{FE}$$

(3)

where  $N_{\rm D}$  is the doping concentration of the semiconductor material,  $W_{\rm D}$  is the depletion width, and  $E_{\rm FE}$  is the electric field across the FE layer. Note that  $Q^*$  here may be overlapped with Q' partly but they should be different in total.

Combining (2) and (3), it is understandable that OS material with larger doping concentration and thickness can provide more space charges, hence resulting in a larger MW. It is known that the electron concentration in InO ( $\sim 10^{20}$ ) [39], [40] is much larger than that in ZnO ( $\sim 10^{18}$ ) [41], [42], [43] and that in IGZO ( $\sim 10^{17}$ ) is smallest [44], [45] among three kinds of OS materials. The screening length decreases with increasing doping concentration, resulting in stronger electric fields across the FE film which enable more complete polarization switching [46], [47]. So, the largest MW is obtained in InO-FeFETs though the InO layer is thinnest. And no MW is done in IGZO-FeFETs due to much fewer space charges. Meanwhile, annealing process such as PCA is benefit to suppress interface traps and hence the clockwise hysteresis can be reduced. Therefore, the MW of devices with PCA is larger than that with PDA. It is worth noting that the MW will be enhanced if more positive charges can be supplied from IL tunneling [48], [49] or from metal introducing and removing at the interface between the FE and channel layer as reported [20]. And  $P_r$  in the FE layer will show an effect if sufficient positive charges can be supplied for full polarization switching.

# V. CONCLUSION

In this study, we have systematically investigated the dominant factors influencing the MW in IL-free OS-FeFETs. Our experimental and theoretical analyses reveal that the MW is primarily governed by the positive charge supply capability of the OS layer and the interface properties between the FE layer and the semiconductor rather than  $P_{\rm r}$  of the HZO layer. Higher doping concentrations of channel material could supply

more positive space charges and hence enhance the MW. Meanwhile, although PCA process could both improve  $P_r$  in FE layer and suppress the interface charge trapping/detrapping, its benefit to MW lies in the later effect. These findings provide valuable insights for the design and optimization of HZO-based OS-FeFETs, emphasizing the need to engineer the positive charge supply at the interface and within the channel to achieve enhanced memory performance.

#### **A**CKNOWLEDGMENT

The authors would like to thank Yuyan Fan and Haoran Zhao for providing critical experimental data in response to reviewers' comments.

#### REFERENCES

- [1] C.-C. Lu et al., "Demonstration of ferroelectric FET memory with oxide semiconductor channel to achieve smallest cell area  $0.009~\mu\text{m}^2$  and high endurance for non-volatile high-bandwidth memory applications," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2024, pp. 1–4, doi: 10.1109/iedm 50854.2024.10873402.

- [2] F. Mo, X. Mei, T. Saraya, T. Hiramoto, and M. Kobayashi, "A simulation study on memory characteristics of InGaZnO-channel ferroelectric FETs with 2D planar and 3D structures," *Japanese J. Appl. Phys.*, vol. 61, no. SC, May 2022, Art. no. SC1013, doi: 10.35848/1347-4065/ac3d0e.

- [3] M.-K. Kim, I.-J. Kim, and J.-S. Lee, "CMOS-compatible ferroelectric NAND flash memory for high-density, low-power, and high-speed threedimensional memory," Sci. Adv., vol. 7, no. 3, p. 1341, Jan. 2021, doi: 10.1126/sciadv.abe1341.

- [4] C.-K. Chen et al., "First demonstration of ultra-low D<sub>it</sub> top-gated ferroelectric oxide-semiconductor memtransistor with record performance by channel defect self-compensation effect for BEOL-compatible nonvolatile logic switch," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2022, pp. 6.1.1–6.1.4, doi: 10.1109/IEDM45625.2022.10019440.

- [5] S. Oh, J. Song, I. K. Yoo, and H. Hwang, "Improved endurance of HfO<sub>2</sub>-based metal-ferroelectric-insulator-silicon structure by highpressure hydrogen annealing," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1092–1095, Jul. 2019, doi: 10.1109/LED.2019.2914700.

- [6] A. J. Tan et al., "Ferroelectric HfO<sub>2</sub> memory transistors with highκ interfacial layer and write endurance exceeding 10<sup>10</sup> cycles," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 994–997, Jul. 2021, doi: 10.1109/LED.2021.3083219.

- [7] Y. Zhou, W. Huang, R. Zhu, R. Huang, and K. Tang, "A reliable 2 bit MLC FeFET with high uniformity and 10<sup>9</sup> endurance by gate stack and write pulse co-optimization," in *Proc. IEEE Eur. Solid-State Electron. Res. Conf. (ESSERC)*, Sep. 2024, pp. 657–660, doi: 10.1109/ESSERC62670.2024.10719462.

- [8] H. Shao et al., "First demonstration of high throughput and reliable homomorphic encryption using FeFET arrays for resource-limited IoT clients," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2024, pp. 1–4, doi: 10.1109/IEDM50854.2024.10873504.

- [9] G. He, M. Liu, L. Q. Zhu, M. Chang, Q. Fang, and L. D. Zhang, "Effect of postdeposition annealing on the thermal stability and structural characteristics of sputtered HfO<sub>2</sub> films on Si (100)," *Surf. Sci.*, vol. 576, nos. 1–3, pp. 67–75, Feb. 2005, doi: 10.1016/j.susc.2004.11.042.

- [10] S. Zhao et al., "Experimental extraction and simulation of charge trapping during endurance of FeFET with TiN/HfZrO/SiO<sub>2</sub>/Si (MFIS) gate structure," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1561–1567, Mar. 2022, doi: 10.1109/TED.2021.3139285.

- [11] J. Duan et al., "Trap generation in whole gate stacks of FeFET with TiN/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/SiO<sub>x</sub>/Si (MFIS) gate structure during endurance fatigue," *IEEE Trans. Electron Devices*, vol. 69, no. 12, pp. 6547–6551, Dec. 2022, doi: 10.1109/TED.2022.3215935.

- [12] S. Dai et al., "Role of nitrogen in suppressing interfacial states generation and improving endurance in ferroelectric field-effect transistors," *IEEE Trans. Electron Devices*, vol. 71, no. 8, pp. 5081–5088, Aug. 2024, doi: 10.1109/TED.2024.3409203.

- [13] F. Tian et al., "Impact of interlayer and ferroelectric materials on charge trapping during endurance fatigue of FeFET with TiN/Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub>/interlayer/Si (MFIS) gate structure," *IEEE Trans. Electron Devices*, vol. 68, no. 11, pp. 5872–5878, Nov. 2021, doi: 10.1109/TED.2021.3114663.

- [14] J. Müller et al., "High endurance strategies for hafnium oxide based ferroelectric field effect transistor," in *Proc. 16th Non-Volatile Memory Technol. Symp. (NVMTS)*, Oct. 2016, pp. 1–7, doi: 10.1109/NVMTS.2016.7781517.

- [15] D. Kleimaier et al., "Charge trapping and endurance degradation in ferroelectric field-effect transistors," in *Proc. 22nd Non-Volatile Memory Technol. Symp. (NVMTS)*, Oct. 2024, pp. 1–5, doi: 10.1109/IEEECONF63530.2024.10830836.

- [16] F. Mo et al., "Experimental demonstration of ferroelectric HfO<sub>2</sub> FET with ultrathin-body IGZO for high-density and low-power memory application," in *Proc. Symp. VLSI Technol.*, Kyoto, Japan, Jun. 2019, pp. T42–T43, doi: 10.23919/VLSIT.2019.8776553.

- [17] Z. Chen et al., "Novel design strategy for high-endurance (> 10<sup>10</sup>) and fast-erase oxide-semiconductor channel FeFET," in *IEDM Tech. Dig.*, San Francisco, CA, USA: IEEE, Dec. 2024, pp. 1–4, doi: 10.1109/IEDM50854.2024.10873449.

- [18] Y. Feng et al., "First demonstration of BEOL-compatible 3D vertical FeNOR," in *Proc. IEEE Symp. VLSI Technol. Circuits* (*VLSI Technol. Circuits*), Honolulu, HI, USA, Jun. 2024, pp. 1–2, doi: 10.1109/VLSITECHNOLOGYANDCIR46783.2024. 10631352.

- [19] Z. Lin et al., "Highly robust all-oxide transistors toward vertical logic and memory," *IEEE Trans. Electron Devices*, vol. 71, no. 12, pp. 7984–7991, Dec. 2024, doi: 10.1109/TED.2024. 3495632.

- [20] T. Cui et al., "Can interface layer be really free for Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> based ferroelectric field-effect transistors with oxide semiconductor channel?" *IEEE Electron Device Lett.*, vol. 45, no. 3, pp. 368–371, Mar. 2024, doi: 10.1109/LED.2024.3355523.

- [21] M. Si, Z. Lin, J. Noh, J. Li, W. Chung, and P. D. Ye, "The impact of channel semiconductor on the memory characteristics of ferroelectric field-effect transistors," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 846–849, 2020, doi: 10.1109/JEDS.2020.3012901.

- [22] M. Si and P. D. Ye, "The critical role of charge balance on the memory characteristics of ferroelectric field-effect transistors," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 5108–5113, Oct. 2021, doi: 10.1109/TED.2021.3108441.

- [23] S. Yoo et al., "Highly enhanced memory window of 17.8 V in ferroelectric FET with IGZO channel via introduction of intermediate oxygen-deficient channel and gate interlayer," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Honolulu, HI, USA, Jun. 2024, pp. 1–2, doi: 10.1109/VLSITECHNOLOGYAND-CIR46783.2024.10631534.

- [24] F. Mo et al., "Low-voltage operating ferroelectric FET with ultrathin IGZO channel for high-density memory application," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 717–723, 2020, doi: 10.1109/JEDS.2020.3008789.

- [25] X. Wang et al., "Comprehensive experiments and modeling applicable for ferroelectric transistors with an MFMIS structure and a wide range of area ratios: Unveiling the operation mechanisms," *IEEE Trans. Electron Devices*, vol. 71, no. 9, pp. 5332–5338, Sep. 2024, doi: 10.1109/TED.2024.3421180.

- [26] T. Cui et al., "A metastable temperature-strain phase diagram of  $Hf_xZr_{1-x}O_2$  thin films based on synchrotron-based in situ 2D GIXRD investigation," *Appl. Phys. Lett.*, vol. 125, no. 25, Dec. 2024, Art. no. 252903, doi: 10.1063/5.0239139.

- [27] X. Wang et al., "Understanding the effect of top electrode on ferroelectricity in atomic layer deposited Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films," ACS Appl. Mater. Interface, vol. 15, no. 12, pp. 15657–15667, Mar. 2023, doi: 10.1021/acsami.2c22263.

- [28] H. Yang et al., "Exploration of structural influences on the ferroelectric switching characteristics of ferroelectric thin-film transistors," *Nanoscale*, vol. 16, no. 42, pp. 19856–19864, 2024, doi: 10.1039/d4nr02096k.

- [29] K. Lee, S. Kim, M. Kim, J.-H. Lee, D. Kwon, and B.-G. Park, "Comprehensive TCAD-based validation of interface trap-assisted ferroelectric polarization in ferroelectric-gate field-effect transistor memory," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1048–1053, Mar. 2022, doi: 10.1109/TED.2022.3144965.

- [30] A. Chouprik et al., "Wake-up in a Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> film: A cycle-by-cycle emergence of the remnant polarization via the domain depinning and the vanishing of the anomalous polarization switching," ACS Appl. Electron. Mater., vol. 1, no. 3, pp. 275–287, Mar. 2019, doi: 10.1021/acsaelm.8b00046.

- [31] C. Jin, C. J. Su, Y. J. Lee, P. J. Sung, T. Hiramoto, and M. Kobayashi, "Study on the roles of charge trapping and fixed charge on subthreshold characteristics of FeFETs," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1304–1312, Mar. 2021, doi: 10.1109/TED.2020.3048916.

- [32] M. Kobayashi et al., "Performance and reliability of nanosheet oxide semiconductor FETs with ALD-grown InGaO for 3D integration (invited)," in *Proc. IEEE Int. Rel. Phys. Symp.* (IRPS), Grapevine, TX, USA, Apr. 2024, pp. 9A.1-1–9A.1-6, doi: 10.1109/IRPS48228.2024.10529363.

- [33] S.-G. Koh, T. Miyasako, T. Hosokura, and E. Tokumitsu, "Impact of ambient moisture on gate controllability in ferroelectric-gate field-effect transistors with bottom-gate geometry," *Jpn. J. Appl. Phys.*, vol. 63, no. 8, Aug. 2024, Art. no. 08SP06, doi: 10.35848/1347-4065/ad66d8.

- [34] P. Nurmamat and A. Abliz, "Rational design of different Ga content bilayer InGaZnO thin-film transistors with Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> passivation layer," *IEEE Trans. Electron Devices*, vol. 71, no. 5, pp. 3032–3038, May 2024, doi: 10.1109/TED.2024.3383429.

- [35] J. H. W. De Wit, G. Van Unen, and M. Lahey, "Electron concentration and mobility in In<sub>2</sub>O<sub>3</sub>," *J. Phys. Chem. Solids*, vol. 38, no. 8, pp. 819–824, Jan. 1977, doi: 10.1016/0022-3697(77)90117-2.

- [36] L.-M. Tang, L.-L. Wang, D. Wang, J.-Z. Liu, and K.-Q. Chen, "Donor-donor binding in In<sub>2</sub>O<sub>3</sub>: Engineering shallow donor levels," *J. Appl. Phys.*, vol. 107, no. 8, Apr. 2010, Art. no. 083704, doi: 10.1063/1.3374644.

- [37] H. Liu et al., "Ferroelectric-like behaviors of mobile-ionic field-effect transistors with amorphous dielectrics," in *Proc. 7th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Mar. 2023, pp. 1–3, doi: 10.1109/EDTM55494.2023.10102947.

- [38] J. Chen et al., "A physics-based model for mobile-ionic field-effect transistors with steep subthreshold swing," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 706–711, 2022, doi: 10.1109/JEDS.2022.3202928.

- [39] L. Liu et al., "Theoretical study of oxygen-vacancy distribution in In<sub>2</sub>O<sub>3</sub>," J. Phys. Chem. C, vol. 125, no. 13, pp. 7077–7085, Apr. 2021, doi: 10.1021/acs.jpcc.1c01462.

- [40] J. A. Libera, J. N. Hryn, and J. W. Elam, "Indium oxide atomic layer deposition facilitated by the synergy between oxygen and water," *Chem. Mater.*, vol. 23, no. 8, pp. 2150–2158, Apr. 2011, doi: 10.1021/cm103637t.

- [41] S. Kwon et al., "Characteristics of the ZnO thin film transistor by atomic layer deposition at various temperatures," *Semicond. Sci. Technol.*, vol. 24, no. 3, Mar. 2009, Art. no. 035015, doi: 10.1088/0268-1242/24/3/035015.

- [42] E. Guziewicz et al., "ALD grown zinc oxide with controllable electrical properties," Semiconductor Sci. Technol., vol. 27, no. 7, Jul. 2012, Art. no. 074011, doi: 10.1088/0268-1242/27/7/074011.

- [43] S. Bang, S. Lee, J. Park, S. Park, W. Jeong, and H. Jeon, "Investigation of the effects of interface carrier concentration on ZnO thin film transistors fabricated by atomic layer deposition," *J. Phys. D, Appl. Phys.*, vol. 42, no. 23, Dec. 2009, Art. no. 235102, doi: 10.1088/0022-3727/42/23/235102

- [44] M.-J. Zhao et al., "Modulation of carrier density in indium—gallium—zinc-oxide thin film prepared by high-power impulse magnetron sputtering," *Vacuum*, vol. 207, Jan. 2023, Art. no. 111640, doi: 10.1016/j.vacuum.2022.111640.

- [45] A. Song, H. M. Hong, K. S. Son, J. H. Lim, and K.-B. Chung, "Hydrogen behavior in top gate amorphous In–Ga–Zn–O device fabrication process during gate insulator deposition and gate insulator etching," *IEEE Trans. Electron Devices*, vol. 68, no. 6, pp. 2723–2728, Jun. 2021, doi: 10.1109/TED.2021.3074120.

- [46] M. Halter et al., "Back-end, CMOS-compatible ferroelectric field-effect transistor for synaptic weights," ACS Appl. Mater. Interface, vol. 12, no. 15, pp. 17725–17732, Apr. 2020, doi: 10.1021/acsami.0c00877.

- [47] X. Wen, M. Halter, L. Bégon-Lours, and M. Luisier, "Physical modeling of HZO-based ferroelectric field-effect transistors with a WO<sub>x</sub> channel," *Frontiers Nanotechnol.*, vol. 4, Aug. 2022, Art. no. 900592, doi: 10.3389/fnano.2022.900592.

- [48] H.-K. Peng, C.-Y. Chan, K.-Y. Chen, and Y.-H. Wu, "Enabling large memory window and high reliability for FeFET memory by integrating AlON interfacial layer," *Appl. Phys. Lett.*, vol. 118, no. 10, Mar. 2021, Art. no. 103503, doi: 10.1063/5.0036824.

- [49] N. Tasneem et al., "The impacts of ferroelectric and interfacial layer thicknesses on ferroelectric FET design," *IEEE Electron Device Lett.*, vol. 42, no. 8, pp. 1156–1159, Aug. 2021, doi: 10.1109/LED.2021.3088388.