# Alleviation of Self-Heating Effect in Top-Gated Ultrathin In<sub>2</sub>O<sub>3</sub> FETs Using a Thermal Adhesion Layer

Pai-Ying Liao<sup>®</sup>, Krutarth Khot<sup>®</sup>, Sami Alajlouni<sup>®</sup>, Mike Snure, Jinhyun Noh<sup>®</sup>, Mengwei Si<sup>®</sup>, *Member, IEEE*, Zhuocheng Zhang<sup>®</sup>, Ali Shakouri, Xiulin Ruan, and Peide D. Ye<sup>®</sup>, *Fellow, IEEE*

Abstract—In this work, a thin layer of hexagonal boron nitride (h-BN) or HfO2 serves as an adhesion layer between the ultrathin atomic-layer-deposited (ALD) indium oxide (In<sub>2</sub>O<sub>3</sub>) channel and a sapphire substrate to enhance the thermal interfacial conductance. A thermo-reflectance (TR) measurement system with high spatial resolution is introduced to experimentally demonstrates the improvement. With the thin h-BN or HfO<sub>2</sub> interlayer, the temperature elevation ( $\Delta T$ ) induced by self-heating effect (SHE) is decreased by roughly 9% or 27%, respectively. To quantify the improvement of the interfacial heat transfer, a steady-state thermal diffusion model with a finite-element method is combined with the experimental TR observation to extract the effective thermal boundary conductance (TBC) values in each case. It is shown that the effective TBC is ameliorated by a factor of 2 or 7 with the h-BN or HfO<sub>2</sub> interlayer, which is responsible for the  $\Delta T$  reduction. Furthermore, phonon density of states (PDOS) distribution mismatch implies that the intersection over union (IOU) ratio in the acoustic phonon region of In<sub>2</sub>O<sub>3</sub> with h-BN or HfO<sub>2</sub> is roughly 3 or 11 times higher than that directly with sapphire, which is responsible for the profound TBC enhancement. Based on this, ultrahigh maximum drain current of 2.4 mA/ $\mu$ m is achieved with 2.1-nm-thick In<sub>2</sub>O<sub>3</sub> channel on a sapphire substrate with an HfO<sub>2</sub> interlayer in between due to the alleviated SHE.

Index Terms—Back-end-of-line (BEOL), indium oxide  $(ln_2O_3)$ , oxide semiconductors, self-heating effect (SHE).

Manuscript received 23 August 2022; revised 20 October 2022; accepted 7 November 2022. Date of publication 18 November 2022; date of current version 3 January 2023. This work was supported in part by the Semiconductor Research Corporation (SRC), Nanoelectronic Computing REsearch (nCORE), Innovative Materials and Processes for Accelerated Compute Technologies (IMPACT) Center; and in part by the SRC/Defense Advanced Research Projects Agency (DARPA), Joint University Microelectronics Program (JUMP) Applications and Systems Driven Center for Energy-Efficient Integrated NanoTechnologies (ASCENT) Center. The review of this article was arranged by Editor J.-S. Park. (*Corresponding author: Peide D. Ye.*)

Pai-Ying Liao, Sami Alajlouni, Jinhyun Noh, Mengwei Si, Zhuocheng Zhang, Ali Shakouri, and Peide D. Ye are with the School of Electrical and Computer Engineering and the Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Krutarth Khot and Xiulin Ruan are with the School of Mechanical Engineering, Purdue University, West Lafayette, IN 47907 USA.

Mike Snure is with the Air Force Research Laboratory, Sensors Directorate, Wright-Patterson AFB, Greene, OH 45433 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3221358.

Digital Object Identifier 10.1109/TED.2022.3221358

# I. INTRODUCTION

**I** N THE past few decades, oxide semiconductors have received continuous attention and been broadly explored in thin-film transistor (TFT) applications [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12]. Owing to their remarkable properties including low fabrication thermal budget, high carrier mobility, atomically smooth surface roughness, and wafer-level scalability, indium oxide  $(In_2O_3)$  [1], [2], [3], [4], [5], [6], [7] and doped indium oxides [8], [9], [10], [11], [12], [13] are especially considered as promising channel materials for next-generation back-end-of-line (BEOL) compatible transistors for monolithic three-dimensional (3-D) integration [14], [15], [16], [17], [18] in recent years.

In<sub>2</sub>O<sub>3</sub> has a wide bandgap of roughly 2.9 eV [19]. Due to its exceptional conformality and thickness control enabled by atomic layer deposition (ALD), scaled In<sub>2</sub>O<sub>3</sub> transistors have been investigated extensively [1], [2], [3], [4], [5], [6], [7]. It has been reported that the channel thickness ( $T_{ch}$ ) of In<sub>2</sub>O<sub>3</sub> transistors can be down to 0.5 nm, which is as thin as a couple of atoms [1], [2]. On the other hand, the drain current ( $I_D$ ) of enhancement-mode (E-mode) In<sub>2</sub>O<sub>3</sub> transistors with  $T_{ch}$  of 1.5 nm, channel length ( $L_{ch}$ ) of 40 nm, and a back-gate (BG) structure can be up to 2.2 mA/ $\mu$ m at drain voltage ( $V_{DS}$ ) of 0.7 V [4], [5].

Nevertheless, In<sub>2</sub>O<sub>3</sub> devices with top-gate (TG) structures are rarely explored in literature since most of the studies concentrate on BG devices, even though transistors with TG structures are especially needed in practical applications [1], [2], [3], [4], [5]. There are two major difficulties for TG In<sub>2</sub>O<sub>3</sub> device investigations, the oxygen vacancy induction during the formation of high-k oxide gate dielectric [18] and the performance deterioration caused by the serious self-heating effect (SHE) [6], [7]. For the former, it is proposed that the pulse of Hf precursor may fetch oxygen atoms from the In<sub>2</sub>O<sub>3</sub> channel during the ALD growth of HfO<sub>2</sub> stack, leading to the generation of oxygen defects at the In<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> interface and therefore the degradation of the device transfer characteristics. Fortunately, this issue can be partly overcome by depositing the HfO<sub>2</sub> dielectric layer at relatively low temperature of 120 °C followed by a rapid-thermal-annealing (RTA) treatment

0018-9383 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. at 250 °C–350 °C [18]. For the latter, SHE happens when the power density (PD) of the device is too high. PD is defined as

$$PD = \frac{P}{A} = \frac{I_D \times V_{DS}}{L_{ch} \times W_{ch}}$$

where *P* denotes the power, *A* denotes the channel area,  $I_D$  denotes the drain current,  $V_{DS}$  denotes the drain-to-source bias,  $L_{ch}$  denotes the channel length, and  $W_{ch}$  denotes the channel width. As the applied  $V_{DS}$  is large and the  $I_D$  becomes high, huge amount of thermal energy will be generated at the atomically thin channel. If the heat cannot be dissipated efficiently, the temperature at the channel region will elevate dramatically. Consequently, the local high temperature may degrade not only the channel material and the dielectric layer but also the interface between them, resulting in the unstability of the device and the non-ideal transport characteristics. This phenomenon is therefore called SHE, and it also significantly damages the long-term reliability of the devices [20], [21].

Because of the extensive commercial availability and favorable affordability, silicon dioxide on silicon (SiO<sub>2</sub>/Si) is often employed as the substrate for TG In2O3 transistor fabrication in the previous investigations [1], [2], [3], [4], [5]. However, a substrate with better heat-transfer capability is desired to alleviate the self-heating issue. Sapphire, which has been utilized as the substrate material in other power devices [22], [23], [24], is more thermally advantageous considering its high thermal conductivity ( $\kappa$ ) of 40 W·m<sup>-1</sup>·K<sup>-1</sup> [25] compared with that of SiO<sub>2</sub> (1.5 W·m<sup>-1</sup>·K<sup>-1</sup> [26]). The higher  $\kappa$  of sapphire implies preferable heat dissipation potential. Nonetheless, it is found that the thermal boundary conductance (TBC) at the In<sub>2</sub>O<sub>3</sub>/sapphire interface is far from ideal, limiting the benefits of SHE reduction that sapphire can conduct. Moreover, TBC between wide bandgap semiconductors and high thermal conductivity substrates has been a concern for FET applications in other materials [27], [28], [29], [30]. Therefore, even though thermal management has been applied to In<sub>2</sub>O<sub>3</sub> and other material systems where substrates with higher  $\kappa$  such as sapphire are utilized to assist transferring thermal energy to deal with SHE, additional explorations to thermally improve the interface between the  $In_2O_3$  channel and the substrate are still desired [6], [7], [24]. We can call these efforts as interface thermal engineering.

It is reported that a thermal adhesion layer as thin as 1 nm is sufficient to increase the TBC by more than a factor of 4 at the Au/sapphire interface [31]. Herein, a thin layer of h-BN or ALD HfO<sub>2</sub> is similarly introduced as a thermal adhesion layer between the In<sub>2</sub>O<sub>3</sub> channel and the sapphire substrate. To experimentally demonstrate the difference between devices with and without the presence of an interlayer, a thermoreflectance (TR) measurement system with high spatial resolution is employed to observe the temperature increase ( $\Delta T$ ) caused by SHE. The  $\Delta T$  of TG In<sub>2</sub>O<sub>3</sub> transistors with the h-BN or HfO<sub>2</sub> adhesion layer induced by SHE is shown to drop by 9% or 27%, compared to that without the interlayer. Through heat-transfer simulation and phonon density of state (PDOS) calculation, it is revealed that the TBC at the interface is improved by a factor of 2 or 7, and this is due to the

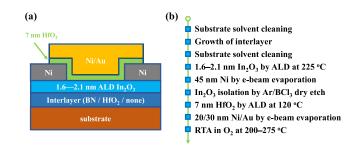

Fig. 1. (a) Cross-sectional illustration of device structure and (b) fabrication flow of TG  $In_2O_3$  transistors with a thermal adhesion interlayer.

higher value of the intersection over union (IOU) ratio in the PDOS acoustic region of  $In_2O_3$  with h-BN or HfO<sub>2</sub> than that with sapphire by a factor of 3 or 11. Consequently, TG  $In_2O_3$  transistors achieving extremely high  $I_D$  of 2.4 mA/ $\mu$ m are realized with  $T_{ch}$  of 2.1 nm,  $L_{ch}$  of 80 nm, and  $W_{ch}$  of 2  $\mu$ m on a sapphire substrate with a thin HfO<sub>2</sub> thermal adhesion layer. Even with such high PD, there is no observable performance degradation due to the reduced SHE.

## **II. EXPERIMENTS**

Fig. 1(a) and (b) illustrates the schematic and fabrication flow of TG  $In_2O_3$  transistors. The substrate was either p+ silicon with 90-nm thermally grown silicon dioxide (SiO<sub>2</sub>/Si) or sapphire. At first, standard solvent cleaning process was applied to the substrates to ensure the surface cleanness. There was no interlayer as SiO<sub>2</sub>/Si served as the substrate while bi-layer (2L) of hexagonal boron nitride (h-BN) or 4 nm of HfO<sub>2</sub> on sapphire served as the substrate. The 2L h-BN was formed by chemical vapor deposition (CVD) while the 4-nm HfO<sub>2</sub> was grown by ALD at 200 °C with [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf) and H<sub>2</sub>O as the Hf and O precursors, respectively. Being limited by CVD process of h-BN on sapphire, only 2L h-BN can be formed instead of thicker h-BN film. Standard solvent cleaning steps were followed again at this point before the deposition of the channel layer.

An 1.6–2.1 nm of In<sub>2</sub>O<sub>3</sub> ultrathin film was conformally grown by ALD at 225 °C with trimethylindium (TMIn) and  $H_2O$  as the In and O precursors, respectively, on the wellcleaned substrates with or without an interlayer, followed by an Ar/BCl<sub>3</sub> plasma dry-etch step for channel region isolation. Next, 45 nm of Ni as source and drain (S/D) contacts with variant  $L_{ch}$  was formed by e-beam lithography (EBL), e-beam deposition, and a lift-off process. At the step of EBL patterning, diluted ZEP 520A served as the e-beam resist. With a sapphire substrate, DisCharge H<sub>2</sub>O was applied as an anti-charging agent on top of the e-beam resist because of the electrical insulation property of sapphire. The anticharging agent was removed by 2-propanol (isopropyl alcohol, IPA) before development. Then, 7-nm HfO<sub>2</sub> as TG dielectric layer was deposited by ALD at 120 °C where the relatively low temperature was for the minimization of the interaction between the HfO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> layers as mentioned. On the top, a Ni/Au of 20-/30-nm metal stack as the gate contact was defined by the identical process as the S/D contacts.

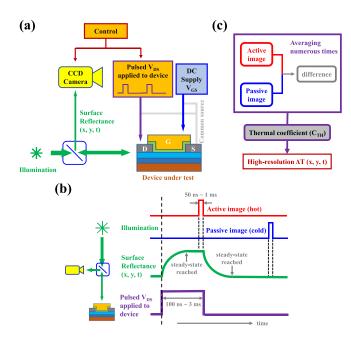

Fig. 2. (a) Schematic of the high spatial resolution TR imaging equipment setup. (b) Working mechanism of the TR measurement system in time domain. (c) Transformation process from TR signal to a temperature scale.

The whole fabrication flow ended with an RTA treatment at 200 °C–275 °C for 2 min in an O<sub>2</sub> environment to annihilate the oxygen vacancies. Dedicated ALD chambers for HfO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> growth were utilized to circumvent cross-contamination throughout the steps, and the thickness of HfO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> films were measured by Gaertner L116A ellipsometer calibrated by transmission electron microscopy (TEM) and atomic force microscopy (AFM) as presented in our previous reports [1], [2], [3], [17], [18].

Fig. 2(a) exhibits the setup of the high-resolution TR measurement system employed to quantitatively explore and address the SHE in this work. Periodic  $V_{DS}$  pulses and a direct-current (dc) gate-to-source ( $V_{GS}$ ) bias are applied to the device under test by dedicated suppliers to generate heat. Besides, high-speed green LED pulses (wavelength of 530 nm) are adopted to illuminate the device, and a synchronized charge-coupled device (CCD) camera is used to capture the surface reflectance.

Fig. 2(b) reveals the working mechanism of the system in time domain. As a  $V_{DS}$  pulse starts, the device is turned on and therefore heated up. After the steady state is reached, TR signal is captured by the synchronized CCD camera as an active image. On the other hand, at the end of the  $V_{DS}$  pulse, the device is turned off and consequently cooled down. After the steady state is reached, TR signal is captured as a passive image. This process is repeated numerous times, and the difference between the active and passive images is averaged accordingly to maximize the signal-to-noise ratio as illustrated in Fig. 2(c). The TR signal is transformed into a temperature scale through diving the values by the calibrated TR coefficient of the surface material ( $C_{TH,Au} = -2.5 \times 10^{-4} \text{ K}^{-1}$ ) to obtain the final thermal image [23], [32], [33].

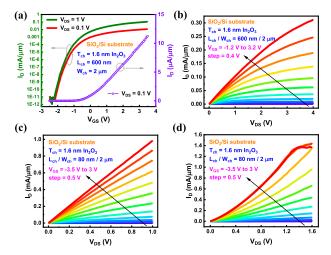

Fig. 3. (a) Transfer and (b) output characteristics of a TG  $In_2O_3$  transistor with a long  $L_{ch}$  of 600 nm on a SiO<sub>2</sub>/Si substrate, exhibiting large ON–OFF ratio of more than 11 orders. Output characteristics of a TG  $In_2O_3$  transistor with a short  $L_{ch}$  of 80 nm and  $V_{DS}$  of (c) 1.0 and (d) 1.6 V on a SiO<sub>2</sub>/Si substrate. Severe SHE degrades the device performance in (d).

### III. RESULTS AND DISCUSSION

Fig. 3(a) and (b) shows the transfer and output characteristics of a representative TG  $In_2O_3$  transistor with  $T_{ch}$  of 1.6 nm, long  $L_{ch}$  of 600 nm, and  $W_{ch}$  of 2  $\mu$ m on a SiO<sub>2</sub>/Si substrate, respectively. The device operates at E-mode with threshold voltage of 0.08 V, and the subthreshold swing (SS) is as low as 150 mV/dec. The ON-OFF ratio is larger than 11 orders of magnitude, specifying decent switching behaviors. Fig. 3(c) and (d) exhibits the output characteristics of a TG  $In_2O_3$  transistor with  $T_{ch}$  of 1.6 nm, short  $L_{ch}$  of 80 nm, and  $W_{\rm ch}$  of 2  $\mu$ m on a SiO<sub>2</sub>/Si substrate, and  $V_{\rm DS}$  applied are 1.0 and 1.6 V, respectively. The  $V_{\rm GS}$  sweeps from -3.5 to 3 V with a 0.5-V step, and the maximum  $I_D$  achieves 1 mA/ $\mu$ m at  $V_{\rm GS}$  of 3 V and  $V_{\rm DS}$  of 1 V. Nevertheless, as  $V_{\rm DS}$  is enlarged to 1.6 V, the  $I_D - V_{DS}$  curves appear in Schottky-like shapes and gradually start dropping with the increased  $V_{GS}$ . This implies the unstability of the device due to the severe SHE.

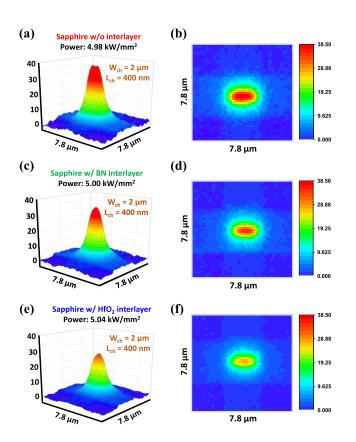

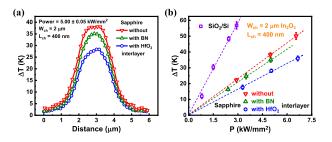

Sapphire, given much higher thermal conductivity compared to  $SiO_2$ , is utilized to replace  $SiO_2/Si$  as the substrate to assist alleviating the acute SHE. However, because of its inferior TBC with the  $In_2O_3$  stack, the heat-transfer capability of sapphire is restricted to some degree. Therefore, a thermal adhesion layer of h-BN or HfO2 is inserted in between to enhance the effective TBC. Fig. 4(a) and (b) exhibits the  $\Delta T$ distribution around the channel region of a TG In<sub>2</sub>O<sub>3</sub> transistor on a sapphire substrate with  $L_{ch}$  of 400 nm,  $W_{ch}$  of 2  $\mu$ m, and no interlayer at PD of approximately 5 kW/mm<sup>2</sup> in a 3-D plot and a heat map, respectively. Likewise, Fig. 4(c)-(f) presents the devices with identical structure and dimensions but an inserted layer of h-BN or HfO<sub>2</sub> at similar PD. In all the three cases, the  $\Delta T$  distributes in bell-like shapes with high plateaus in the middle of the device, descending to their proximity. It is noticeable that the device without a thermal adhesion layer shows the highest  $\Delta T$  while the one with an HfO<sub>2</sub> interlayer exhibits the lowest.

For a clearer comparison, the cross sections of Fig. 4(b), (d), and (f) along the direction of channel width are plotted into

Fig. 4.  $\Delta T$  (a) 3-D plot and (b) heat map of a TG In<sub>2</sub>O<sub>3</sub> transistor with  $W_{ch}$  of 2  $\mu$ m,  $L_{ch}$  of 400 nm, and no interlayer on a sapphire substrate at PD of roughly 5 kW/mm<sup>2</sup> imaged by the TR measurement system. The corresponding plots of the devices with the same structure, dimensions, but a thermal adhesion layer of (c) and (d) 2L h-BN, and (e) and (f) 4-nm HfO<sub>2</sub> at similar PD.

Fig. 5. (a) Cross sections of the three  $\Delta T$  plots along the direction of channel width, showing 9% or 27% alleviation of the SHE by inserting a thermal adhesion layer of h-BN or HfO<sub>2</sub>, respectively. (b) Comparison between devices with different substrates and interlayers and variant PD. Great linearity is agreed in all cases.

Fig. 5(a). With identical dimensions and similar PD, the TG In<sub>2</sub>O<sub>3</sub> devices without a thermal adhesion layer, with 2L h-BN, and with 4-nm HfO<sub>2</sub> demonstrate maximum  $\Delta T$  of 38.2, 35.0, and 28.1 K, respectively. This suggests that a 9% or 27% of  $\Delta T$  reduction is obtained by inserting a thin thermal adhesion layer of h-BN or HfO<sub>2</sub> between the In<sub>2</sub>O<sub>3</sub> channel and the sapphire substrate. Besides, the maximum  $\Delta T$  with cases of different substrates and interlayers at variant PD is arranged into Fig. 5(b) where the error bars indicate 95% confidence intervals. Observably, the maximum  $\Delta T$  of a certain device

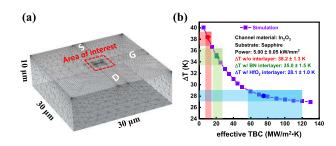

Fig. 6. (a) Mesh build-up of the thermal diffusion model for heat transfer simulation with a finite-element method. The area of interest is indicated by the red-dashed square. (b) Maximum  $\Delta T$  at the steady state extracted by setting variant effective TBC. Considering the experimental  $\Delta T$  error ranges, ranges of effective TBCs are corresponded accordingly.

is roughly proportional to the PD in all cases. Moreover, at the same PD, the  $\Delta T$  decreases by a factor of 2.5 through replacing the SiO<sub>2</sub>/Si substrate with sapphire and by a factor of 2.8 or 3.7 through replacing that with BN/sapphire or HfO<sub>2</sub>/sapphire, respectively. This specifies the alleviation of SHE in TG In<sub>2</sub>O<sub>3</sub> transistors by interface thermal engineering.

Although h-BN has much higher thermal conductivity  $(390 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1} \text{ [34]})$  than HfO<sub>2</sub> (1.2 W $\cdot \text{m}^{-1} \cdot \text{K}^{-1} \text{ [35]})$ , devices with HfO<sub>2</sub> interlayer performs  $3 \times \text{larger } \Delta T$  reduction. This suggests that the thermal interfacial conductance is significant here. The insertion of the thermal adhesion layer eliminates the interface of In<sub>2</sub>O<sub>3</sub>/sapphire but brings in another two interfaces of In<sub>2</sub>O<sub>3</sub>/interlayer and interlayer/sapphire. By the TR imaging and maximum  $\Delta T$  comparison discussed, it is observable that the effective TBC of the devices with a h-BN or HfO<sub>2</sub> interlayer is larger than the TBC of the devices without one. To quantify the improvement, a steadystate thermal diffusion model with a finite-element method is combined with the TR imaging results to extract the effective TBC values. It is verified in literature that this method of TBC extraction is consistent with experimentally measured TBC values [36], [37].

The steady-state thermal simulation is carried out through COMSOL Multiphysics which adopts a finite-element method. Fig. 6(a) demonstrates the mesh build-up of the model which is designed to have identical structures and dimensions ( $L_{ch}$  of 400 nm and  $W_{ch}$  of 2  $\mu$ m) with the devices used in Fig. 3. The PD is set to be around 5 kW/mm<sup>2</sup> which is the same as the scenarios in Fig. 3 as well, and the square indicated by the red dashed lines denotes the area of interest which includes the channel region and its proximity. By giving variant effective TBC values of the introduced interfaces, different values of maximum  $\Delta T$  are obtained as shown in Fig. 6(b). Considering the experimental  $\Delta T$  values with the error ranges, the corresponding TBC implied by the steady-state simulation for the devices without an interlayer is extracted to be 11 + 4/-4 MW/(m<sup>2</sup>·K). Similarly, the effective TBC of the devices with a thermal adhesion layer of h-BN or HfO<sub>2</sub> is extracted to be 21 + 6/-5 MW/(m<sup>2</sup>·K) or 75 + 45/-19 MW/(m<sup>2</sup>·K), which is 2 or 7 times larger than the original value, respectively. The huge improvement of effective TBC suggests that the interlayer of h-BN or HfO<sub>2</sub> enhances the heat dissipation that sapphire is capable of, benefiting the SHE alleviation in TG In<sub>2</sub>O<sub>3</sub> transistors.

The obtained effective TBC, including contributions from both the introduced interfaces and the interlayer itself, equals to the inverse of the sum of the inversed thermal conductance of the three contributions. The thermal conductance of the interlayer itself is defined as the thermal conductivity divided by the thickness. It is revealed that thermal conductivity of a thin film is more dependent on its thickness as the thickness is down to the same order of magnitude of the energy carriers' mean free path [38], [39]. Considering the thin-film thermal conductivity of the 4-nm HfO2  $(0.5-1.0 \text{ W}\cdot\text{m}^{-1}\cdot\text{K}^{-1} \text{ [40]})$  or 2L h-BN (out-of-plane thermal conductivity 2.3–3.5  $W \cdot m^{-1} \cdot K^{-1}$  [41]) thermal adhesion layer, the TBC contribution from the interlayer itself is roughly  $125-250 \text{ MW}/(\text{m}^2 \cdot \text{K})$  or  $1900-3500 \text{ MW}/(\text{m}^2 \cdot \text{K})$ , respectively. The TBC contributions are larger than their individual effective TBC values, indicating that the interlayer itself may not be a critical thermal bottleneck for the effective TBC in either case.

Beside the interlayer itself, there are two introduced interfaces by the insertion of the interlayer, namely, interlayer/sapphire and  $In_2O_3$ /interlayer. For the former, the experimentally demonstrated TBC of HfO<sub>2</sub>/sapphire interface by time-domain TR (TDTR) is around 227–327 MW/(m<sup>2</sup>·K) [36], which is much larger than the effective TBC of 75 MW/(m<sup>2</sup>·K). Besides, the TBC of h-BN/sapphire is reported to be 980 MW/(m<sup>2</sup>·K) [42] which is also even higher than the effective TBC of 21 MW/(m<sup>2</sup>·K). Consequently, the TBC contribution from the interlayer/sapphire interface is not a main concern in each case, either.

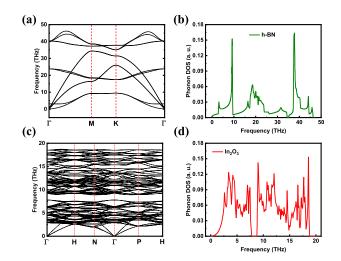

Therefore, the bottleneck of the effective TBC could be the In<sub>2</sub>O<sub>3</sub>/interlayer interface. Here, phonons as the energy carriers play a significant role. Especially, phonons at lower frequency, called acoustic phonons, are attributed to most of the heat transport behaviors [43]. To investigate the behaviors, the PDOS distributions of HfO2 and sapphire were obtained from [36] and [44], and the PDOS distribution calculations of h-BN and In<sub>2</sub>O<sub>3</sub> were performed by density functional theory (DFT) as implemented in Vienna Ab initio Simulation Package (VASP) [45], [46]. The two calculations on h-BN and  $In_2O_3$ followed different pathways due to the differences in their material properties. A bilayer h-BN with vacuum above and below was constructed to replicate the 2L interlayers in the device. The projector augmented wave (PAW) [47] method was adopted along with optB86-vdW [48] functional due to the presence of van der Waals forces based on previous work [49]. An energy cut-off of 600 eV was involved together with a 9  $\times$  9  $\times$  3 Monkhorst-Pack k-point mesh for structure optimization of the four-atom bilayer unit cell. Density functional perturbation theory (DFPT) was applied for calculating the second-order force constants on a  $6 \times 6 \times 1$  supercell with a  $3 \times 3 \times 2$  k-point grid. The required PDOS were acquired using an open-source package Phonopy [50]. The calculated phonon dispersion of 2L h-BN is revealed in Fig. 7(a), and its resultant PDOS distribution is demonstrated in Fig. 7(b). For  $In_2O_3$ , the PAW method was used alongside LDA functional with a cut-off of 520 eV. The 40-atom cubic unit cell was optimized utilizing a  $4 \times 4 \times 4$  Monkhorst-Pack k-point mesh. A supercell of  $2 \times 2 \times 2$  was constructed with a  $2 \times 2 \times 2$  k-point mesh for the second-order force

Fig. 7. Phonon dispersion of (a) h-BN and (c)  $In_2O_3$  performed by DFT calculation and (b) and (d) resultant PDOS distributions of them.

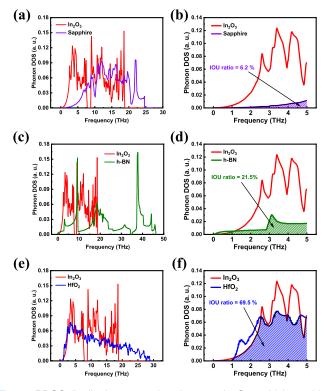

Fig. 8. PDOS distribution comparison between  $In_2O_3$  and (a) sapphire, (c) h-BN, and (e) HfO2 and (b), (d), and (f) their acoustic phonon region magnification (frequency lower than 5 THz). The IOU ratio between PDOS distributions of sapphire, h-BN, and HfO<sub>2</sub> and that of  $In_2O_3$  in the acoustic phonon region are 6.2%, 21.5%, and 69.5%, respectively.

constants calculations. However, DFPT is not applicable for  $In_2O_3$  due to the large computational expense of the method for this complicated structure. Hence, the finite differences method for force constants calculation was adopted instead. Similar to h-BN, Phonopy was employed for post-processing and obtaining the PDOS of  $In_2O_3$ . The calculated phonon dispersion of  $In_2O_3$  is shown in Fig. 7(c), and its resultant PDOS distribution is demonstrated in Fig. 7(d).

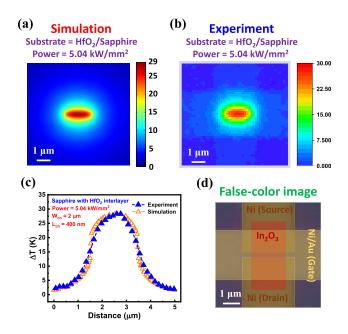

Fig. 9. (a) Simulated  $\Delta T$  distribution around the channel region of a TG  $In_2O_3$  device with  $L_{ch}$  of 400 nm and  $W_{ch}$  of 2  $\mu$ m on a sapphire substrate with HfO<sub>2</sub> interlayer at PD of 5 kW/mm<sub>2</sub>. (b) Experimental  $\Delta T$  distribution of the same region of a transistor with identical structure and dimensions at the same PD imaged by the high-resolution TR equipment. (c) Cross-sectional comparison along the channel width direction of the experimental and simulation results. (d) False-color image of a TG In<sub>2</sub>O<sub>3</sub> transistor with the same structure and dimensions for better visualization of the SHE.

Fig. 8 exhibits the PDOS distributions of sapphire, h-BN, and HfO<sub>2</sub> with that of  $In_2O_3$  where Fig. 8(a), (c), and (e) shows the comparisons of the whole distributions while Fig. 8(b), (d), and (f) illustrates the acoustic region magnification (frequency lower than 5 THz). All the distributions are normalized by setting the integration area to be one (1). IOU ratio is here used to evaluate how well two distributions match with each other and defined as the ratio of their intersection area and their union area. As demonstrated in Fig. 8(b), the IOU ratio between PDOS of sapphire and  $In_2O_3$ in the acoustic phonon region is only 6.2%, explaining the low TBC of 11 + 4/-4 MW/(m<sup>2</sup>·K). On the other hand, Fig. 8(d) and (f) indicates that the IOU ratios in the acoustic phonon region with h-BN and HfO<sub>2</sub> employed are improved to 21.5% and 69.5%, which are 3 and 11 times larger than 6.2%, respectively. Due to the much larger IOU ratios in the acoustic phonon region of the PDOS distributions, heat transfer is much more efficient with the presence of the h-BN or  $HfO_2$  interlayer in TG  $In_2O_3$  devices with a sapphire substrate, especially HfO<sub>2</sub>. Accordingly, the effective TBC of: 1)  $In_2O_3$ /interlayer interface; 2) thin h-BN or HfO<sub>2</sub> stack; and 2) interlayer/sapphire interface as a whole is considered satisfactory and improved from the structure without the thermal adhesion layer, which is responsible for the 9% or 27% of the SHE alleviation observed by the TR imaging, respectively.

With the extracted effective TBC, the steady-state  $\Delta T$  distribution is demonstrated in Fig. 9(a) where the case with HfO<sub>2</sub> interlayer at PD of around 5.04 kW/mm<sup>2</sup> is simulated.

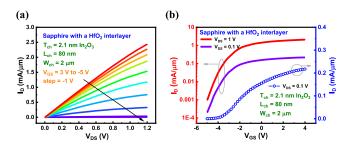

Fig. 10. (a) Output and (b) transfer characteristics of a 2.1-nm-thick TG  $In_2O_3$  transistor with  $L_{ch}$  of 80 nm and  $W_{ch}$  of 2  $\mu$ m on a sapphire substrate with a HfO<sub>2</sub> thermal adhesion layer. Due to the great heat-transfer properties of the substrate, SHE is negligible, and maximum  $I_D$  of 2.4 mA/ $\mu$ m is achieved at  $V_{DS}$  of 1.2 V. The ON–OFF ratio is larger than 3 orders of magnitude.

For clearer comparison, the TR image of Fig. 4(f) is re-plotted with a modified rainbow-color scale into Fig. 9(b) where the device with HfO<sub>2</sub> interlayer at PD of 5.04 kW/mm<sup>2</sup> is measured. Fig. 9(a) and (b) shows in excellent agreement, specifying that the experiments and simulation lead to extremely consistent results and support each other. The cross sections of Fig. 9(a) and (b) along the direction of channel width are revealed in Fig. 9(c). The two curves are alike and only off a little near the edge of the channel where the experimental curve is smoother while the simulation curve is sharper. On the other hand, Fig. 9(d) exhibits a false-color image of a TG In<sub>2</sub>O<sub>3</sub> transistor with the same structure and dimensions. By comparing Fig. 9(a), (b), and (d), it is clear that the heat comes from the channel region of the device and transfers to its proximity in all directions, and the SHE is better visualized.

Therefore, by growing an HfO<sub>2</sub> interfacial layer on a sapphire substrate for thermal adhesion or thermal interface engineering, the SHE of TG  $In_2O_3$  devices is reduced. Fig. 10(a) exhibits the output characteristics of a TG In<sub>2</sub>O<sub>3</sub> transistor with  $T_{ch}$  of 2.1 nm,  $L_{ch}$  of 80 nm, and  $W_{ch}$  of 2  $\mu$ m on an HfO<sub>2</sub>/sapphire substrate where very high  $I_D$  of 2.4 mA/ $\mu$ m is demonstrated at  $V_{DS}$  of 1.2 V. The  $I_D - V_{DS}$  curves are wellperformed with some saturation behaviors at low  $V_{GS}$ , and the SHE is not severe under these bias conditions. Fig. 10(b)reveals the corresponding transfer characteristics where an ON-OFF ratio larger than 3 orders of magnitude is behaved even though the device is in depletion-mode. The solid curves are in logarithmic scale, and the empty symbols represent the identical curve in linear scale. Some key parameters are extracted as follows: threshold voltage  $(V_T)$  being -3.7 V, transconductance  $(g_m)$  being 495  $\mu$ S/ $\mu$ m at  $V_{DS} = 1$  V, and field-effect mobility ( $\mu_{\rm FE}$ ) being 20.9 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>. Note that the degradations of the transfer characteristics and the negative shift of  $V_{\rm T}$  in Fig. 10(b) compared with Fig. 3(a) are not due to the change of substrate but the thicker  $T_{ch}$  and shorter  $L_{\rm ch}$ , as the device performance parameters such as  $V_{\rm T}$ ,  $\mu_{\rm FE}$ , ON-OFF ratio, and SS value of ALD In2O3 transistors sensitively depend on their  $T_{ch}$  and  $L_{ch}$  [1], [2], [3], [4], [6], [18].

Although substrate materials with even higher thermal conductivity such as silicon carbide (SiC, 387  $W \cdot m^{-1} \cdot K^{-1}$ ) [51] and diamond (2200  $W \cdot m^{-1} \cdot K^{-1}$ ) [52] normally have less affordability and relatively limited commercial availability, they are generally advantageous against others for power device applications. Nevertheless, thermal interfacial issues at the channel/substrate interface may also restrict the benefit they can conduct to some degree. This work provides a route to potentially resolve this challenge and maximize the profits that those higher thermal conductivity substrates can bring to relieve SHE.

### **IV. CONCLUSION**

In summary, heat dissipation of TG ultrathin In<sub>2</sub>O<sub>3</sub> transistors on a sapphire substrate with 2L h-BN, 4-nm HfO<sub>2</sub>, or no interlayer is explored to assist alleviating SHE. A high spatial resolution TR measurement system is introduced to visualize the  $\Delta T$  distribution as the devices are at on-state with SHE. With the thermal adhesion layer of h-BN or HfO<sub>2</sub> to improve the interfacial heat transfer between the In<sub>2</sub>O<sub>3</sub> channel and the sapphire substrate, the observed maximum  $\Delta T$  of the devices is reduced by 9% or 27%, respectively. A steady-state thermal diffusion model with a finite-element method is integrated with the TR imaging results to extract the effective TBC values in each case to quantify the improvement of the interfacial heat transfer. The effective TBC is enhanced by a factor of 2 or 7 with the insertion of the h-BN or HfO<sub>2</sub> interlayer. The huge amelioration of the effective TBC is likely due to the better match of the PDOS distribution in the acoustic region where the IOU ratio of In<sub>2</sub>O<sub>3</sub> with h-BN or HfO<sub>2</sub> is 3 or 11 times larger than that with sapphire. Because of the cured SHE, high  $I_D$  of 2.4 mA/ $\mu$ m at  $V_{DS}$  of 1.2 V is realized in a TG In<sub>2</sub>O<sub>3</sub> transistor with ultrathin  $T_{ch}$  of 2.1 nm,  $L_{ch}$  of 80 nm, and  $W_{\rm ch}$  of 2  $\mu$ m on an HfO<sub>2</sub>/sapphire substrate. This thermal engineering method can be potentially applied to other BEOL devices with other thermal engineered adhesion and isolation layers above the standard front-end-of-line Si CMOS circuits.

#### REFERENCES

- M. Si, Z. Lin, Z. Chen, X. Sun, H. Wang, and P. D. Ye, "Scaled indium oxide transistors fabricated using atomic layer deposition," *Nature Electron.*, vol. 5, no. 3, pp. 164–170, Feb. 2022, doi: 10.1038/s41928-022-00718-w.

- [2] M. Si et al., "Why In<sub>2</sub>O<sub>3</sub> can make 0.7 nm atomic layer thin transistors," *Nano Lett.*, vol. 21, no. 4, pp. 500–506, Jan. 2021, doi: 10.1021/acs.nanolett.0c03967.

- [3] M. Si, Z. Lin, A. Charnas, and P. D. Ye, "Scaled atomic-layer-deposited indium oxide nanometer transistors with maximum drain current exceeding 2 A/mm at drain voltage of 0.7 V," *IEEE Electron Device Lett.*, vol. 42, no. 2, pp. 184–187, Feb. 2021, doi: 10.1109/LED.2020.3043430.

- [4] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomiclayer-deposited In<sub>2</sub>O<sub>3</sub> transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: 10.1109/TED.2021.3053229.

- [5] A. Charnas, M. Si, Z. Lin, and P. D. Ye, "Realization of enhancementmode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by room temperature oxygen plasma treatment," *Appl. Phys. Lett.*, vol. 118, no. 5, Feb. 2021, Art. no. 052107, doi: 10.1063/5.0039783.

- [6] P.-Y. Liao, M. Si, Z. Zhang, Z. Lin, and P. D. Ye, "Realization of maximum 2 A/mm drain current on top-gate atomic-layer-thin indium oxide transistors by thermal engineering," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 147–151, Jan. 2022, doi: 10.1109/TED.2021.3125923.

- [7] P.-Y. Liao et al., "Thermal studies of BEOL-compatible top-gated atomically thin ALD In<sub>2</sub>O<sub>3</sub> FETs," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2022, pp. 322–323.

- [8] S. Li et al., "Nanometre-thin indium tin oxide for advanced highperformance electronics," *Nature Mater.*, vol. 18, no. 10, pp. 1091–1097, Oct. 2019, doi: 10.1038/s41563-019-0455-8.

- [9] M. Si et al., "Indium-tin-oxide transistors with one nanometer thick channel and ferroelectric gating," ACS Nano, vol. 14, no. 9, pp. 11542–11547, Sep. 2020, doi: 10.1021/acsnano.0c03978.

- [10] J. Wu, F. Mo, T. Saraya, T. Hiramoto, and M. Kobayashi, "A monolithic 3D integration of RRAM array with oxide semiconductor FET for inmemory computing in quantized neural network AI applications," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [11] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with  $I_{on} = 370 \mu A/\mu m$ , SS = 73mV/dec and  $I_{on}/I_{off}$  ratio >  $4 \times 10^9$ ," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [12] S. Samanta, K. Han, C. Sun, C. Wang, A. V. Thean, and X. Gong, "Amorphous IGZO TFTs featuring extremely-scaled channel thickness and 38 nm channel length: Achieving record high  $G_{m,max}$  of 125  $\mu$ S/ $\mu$ m at V<sub>DS</sub> of 1 V and I<sub>on</sub> of 350  $\mu$ A/ $\mu$ m," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [13] Z. Zhang et al., "Atomically thin indium-tin-oxide transistors enabled by atomic layer deposition," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 231–236, Jan. 2022, doi: 10.1109/TED.2021.3129707.

- [14] S. Fujita and K. Kaneko, "Epitaxial growth of corundum-structured wide band gap III-oxide semiconductor thin films," *J. Cryst. Growth*, vol. 401, pp. 588–592, Sep. 2014, doi: 10.1016/j.jcrysgro.2014.02.032.

- [15] H. Y. Kim et al., "Low-temperature growth of indium oxide thin film by plasma-enhanced atomic layer deposition using liquid dimethyl (Nethoxy-2,2-dimethylpropanamido) indium for high-mobility thin film transistor application," ACS Appl. Mater. Interfaces, vol. 8, no. 40, pp. 26924–26931, Oct. 2016, doi: 10.1021/acsami.6b07332.

- [16] J. Lee et al., "High mobility ultra-thin crystalline indium oxide thin film transistor using atomic layer deposition," *Appl. Phys. Lett.*, vol. 113, no. 11, Sep. 2018, Art. no. 112102, doi: 10.1063/1.5014029.

- [17] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "First demonstration of atomiclayer-deposited BEOL-compatible In<sub>2</sub>O<sub>3</sub> 3D fin transistos and integrated circuits: High mobility of 113 cm<sup>2</sup>/V·s, maximum drain current of 2.5 mA/μm and maximum voltage gain of 38 V/V in In<sub>2</sub>O<sub>3</sub> inverter," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2021, pp. 1–2.

- [18] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "High-performance atomic-layer-deposited indium oxide 3-D transistors and integrated circuits for monolithic 3-D integration," *IEEE Trans. Electron Devices*, vol. 68, no. 12, pp. 6605–6609, Dec. 2021, doi: 10.1109/TED.2021.3106282.

- [19] K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, "Amorphous oxide semiconductors for high-performance flexible thinfilm transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 5, pp. 4303–4308, Apr. 2006, doi: 10.1143/JJAP.45.4303.

- [20] M. H. Wong, Y. Morikawa, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Characterization of channel temperature in Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors by electrical measurements and thermal modeling," *Appl. Phys. Lett.*, vol. 109, no. 19, Nov. 2016, Art. no. 193503, doi: 10.1063/1.4966999.

- [21] R. J. Trew, D. S. Green, and J. B. Shealy, "AlGaN/GaN HFET reliability," *IEEE Microw. Mag.*, vol. 10, no. 4, pp. 116–127, Jun. 2009, doi: 10.1109/MMM.2009.932286.

- [22] R. Gaska, A. Osinsky, J. W. Yang, and M. S. Shur, "Self-heating in high-power AlGaN-GaN HFETs," *IEEE Electron Device Lett.*, vol. 19, no. 3, pp. 89–91, Mar. 1998, doi: 10.1109/55.661174.

- [23] Y. Zhou et al., "Thermal characterization of polycrystalline diamond thin film heat spreaders grown on GaN HEMTs," *Appl. Phys. Lett.*, vol. 111, no. 4, Jul. 2017, Art. no. 041901, doi: 10.1063/1.4995407.

- [24] J. Noh et al., "High performance β-Ga<sub>2</sub>O<sub>3</sub> nano-membrane field effect transistors on a high thermal conductivity diamond substrate," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 914–918, Aug. 2019, doi: 10.1109/JEDS.2019.2933369.

- [25] S. Burghartz and B. Schulz, "Thermophysical properties of sapphire, AlN and MgAl<sub>2</sub>O<sub>3</sub> down to 70 K," *J. Nucl. Mater.*, vols. 212–215, pp. 1065–1068, Sep. 1994, doi: 10.1016/0022-3115(94)90996-2.

- [26] H.-C. Chien, D.-J. Yao, M.-J. Huang, and T.-Y. Chang, "Thermal conductivity measurement and interface thermal resistance estimation using SiO<sub>2</sub> thin film," *Rev. Sci. Instrum.*, vol. 79, no. 5, May 2008, Art. no. 054902, doi: 10.1063/1.2927253.

- [27] X. Li, W. Park, Y. Wang, Y. P. Chen, and X. Ruan, "Reducing interfacial thermal resistance between metal and dielectric materials by a metal interlayer," *J. Appl. Phys.*, vol. 125, no. 4, Jan. 2019, Art. no. 045302, doi: 10.1063/1.5079428.

- IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 70, NO. 1, JANUARY 2023

- [28] B. A. Cola, J. Xu, C. Cheng, X. Xu, T. S. Fisher, and H. Hu, "Photoacoustic characterization of carbon nanotube array thermal interfaces," *J. Appl. Phys.*, vol. 101, no. 5, Mar. 2007, Art. no. 054313, doi: 10.1063/1.2510998.

- [29] C. Dames and G. Chen, "Theoretical phonon thermal conductivity of Si/Ge superlattice nanowires," J. Appl. Phys., vol. 95, no. 2, pp. 682–693, Jan. 2004, doi: 10.1063/1.1631734.

- [30] R. S. Prasher and P. E. Phelan, "A scattering-mediated acoustic mismatch model for the prediction of thermal boundary resistance," *J. Heat Transf.*, vol. 123, no. 1, pp. 105–112, Feb. 2001, doi: 10.1115/1.1338138.

- [31] M. Jeong et al., "Enhancement of thermal conductance at metaldielectric interfaces using subnanometer metal adhesion layers," *Phys. Rev. A, Gen. Phys. Appl.*, vol. 5, no. 1, Jan. 2016, Art. no. 014009, doi: 10.1103/PhysRevApplied.5.014009.

- [32] K. Maize, A. Ziabari, W. D. French, P. Lindorfer, B. Oconnell, and A. Shakouri, "Thermoreflectance CCD imaging of self-heating in power MOSFET arrays," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3047–3053, Sep. 2014, doi: 10.1109/TED.2014.2332466.

- [33] H. Zhou, K. Maize, J. Noh, A. Shakouri, and P. D. Ye, "Thermodynamics studies of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors on a sapphire substrate," ACS Omega, vol. 2, pp. 7723–7729, Nov. 2017, doi: 10.1021/acsomega.7b01313.

- [34] E. K. Sichel, R. E. Miller, M. S. Abrahams, and C. J. Buiocchi, "Heat capacity and thermal conductivity of hexagonal pyrolytic boron nitride," *Phys. Rev. B, Condens. Matter*, vol. 13, no. 10, pp. 4607–4611, May 1976, doi: 10.1103/PhysRevB.13.4607.

- [35] S.-M. Lee, D. G. Cahill, and T. H. Allen, "Thermal conductivity of sputtered oxide films," *Phys. Rev. B, Condens. Matter*, vol. 52, no. 1, pp. 253–257, Jul. 1995, doi: 10.1103/PhysRevB.52.253.

- [36] J. Noh et al., "Enhancement of thermal transfer from β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors to high thermal conductivity substrate by inserting an interlayer," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1186–1190, Jan. 2021, doi: 10.1109/TED.2022.3142651.

- [37] Z. Cheng, L. Yates, J. Shi, M. J. Tadjer, K. D. Hobart, and S. Graham, "Thermal conductance across β-Ga<sub>2</sub>O<sub>3</sub>-diamond van der Waals heterogeneous interfaces," *APL Mater.*, vol. 7, Mar. 2019, Art. no. 031118, doi: 10.1063/1.5089559.

- [38] Y. Zhang, Q. Su, J. Zhu, S. Koirala, S. J. Koester, and X. Wang, "Thickness-dependent thermal conductivity of mechanically exfoliated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films," *Appl. Phys. Lett.*, vol. 116, no. 20, May 2020, Art. no. 202101, doi: 10.1063/5.0004984.

- [39] Y. Volkov, L. Palatnik, and A. Pugachev, "Investigation of the thermal properties of thin aluminum," *Sov. J. Exp. Theor. Phys.*, vol. 43, no. 6, p. 1171, 1976.

- [40] M. A. Panzer et al., "Thermal properties of ultrathin hafnium oxide gate dielectric films," *IEEE Electron Device Lett.*, vol. 30, no. 12, pp. 1269–1271, Oct. 2009, doi: 10.1109/LED.2009.2032937.

- [41] C. Yuan et al., "Modulating the thermal conductivity in hexagonal boron nitride via controlled boron isotope concentration," *Commun. Phys.*, vol. 2, no. 1, pp. 1–8, Dec. 2019, doi: 10.1038/s42005-019-0145-5.

- [42] I. Choi et al., "Application of hexagonal boron nitride to a heattransfer medium of an InGaN/GaN quantum-well green LED," ACS Appl. Mater. Interfaces, vol. 11, no. 20, pp. 18876–18884, May 2019, doi: 10.1021/acsami.9b05320.

- [43] F. P. Incropera, D. P. DeWitt, T. L. Bergman, and A. S. Lavine, *Fundamentals of Heat and Mass Transfer*, 6th ed. Hoboken, NJ, USA: Wiley, 2007.

- [44] D. Ceresoli and D. Vanderbilt, "Structural and dielectric properties of amorphous ZrO<sub>2</sub> and HfO<sub>2</sub>," *Phys. Rev. B, Condens. Matter*, vol. 74, no. 12, Sep. 2006, Art. no. 125108, doi: 10.1103/PhysRevB.74.125108.

- [45] G. Kresse and J. Furthmüller, "Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set," *Phys. Rev. B, Condens. Matter*, vol. 54, p. 11169, Oct. 1996, doi: 10.1103/ PhysRevB.54.11169.

- [46] G. Kresse and D. Joubert, "From ultrasoft pseudopotentials to the projector augmented-wave method," *Phys. Rev. B, Condens. Matter*, vol. 59, p. 1758, Jan. 1999, doi: 10.1103/PhysRevB.59.1758.

- [47] P. E. Blöchl, "Projector augmented-wave method," *Phys. Rev. B*, *Condens. Matter*, vol. 50, p. 17953, Dec. 1994, doi: 10.1103/ PhysRevB.50.17953.

- [48] J. Klimeš, D. R. Bowler, and A. Michaelides, "Van der Waals density functionals applied to solids," *Phys. Rev. B, Condens. Matter*, vol. 83, May 2011, Art. no. 195131, doi: 10.1103/PhysRevB.83.195131.

- [49] G. J. Slotman, G. A. de Wijs, A. Fasolino, and M. I. Katsnelson, "Phonons and electron-phonon coupling in graphene-H-BN heterostructures," *Annalen der Physik*, vol. 526, nos. 9–10, pp. 381–386, Sep. 2014, doi: 10.1002/andp.201400155.

- [50] A. Togo and I. Tanaka, "First principles phonon calculations in materials science," *Scripta Mater.*, vol. 108, pp. 1–5, Nov. 2015, doi: 10.1016/j.scriptamat.2015.07.021.

- [51] E. A. Burgemeister, W. von Muench, and E. Pettenpaul, "Thermal conductivity and electrical properties of 6H silicon carbide," *J. Appl. Phys.*, vol. 50, no. 9, pp. 5790–5794, Sep. 1979, doi: 10.1063/1.326720.

- [52] J. R. Olson, R. O. Pohl, J. W. Vandersande, A. Zoltan, T. R. Anthony, and E. F. Banholzer, "Thermal conductivity of diamond between 170 and 1200 K and the isotope effect," *Phys. Rev. B, Condens. Matter*, vol. 47, no. 22, pp. 14850–14857, Jun. 1993, doi: 10.1103/PhysRevB.47. 14850.