# Multi-Probe Characterization of Ferroelectric/Dielectric Interface by C-V, P-V and Conductance Methods

Junkang Li, Yiming Qu, Mengwei Si, Xiao Lyu, and Peide D. Ye\*

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA. Email: \*yep@purdue.edu

## **Abstract**

In this work, we report on the multi-probe characterization of interfacial charges at the ferroelectric/dielectric (FE/DE) interface in response to both large-signal measurement associated with polarization switching and small-signal measurement without polarization switching. Charge densities at the FE/DE interface are extracted from temperature dependent C-V, P-V, conductance methods. It is found that the charge injection and accumulation at the FE/DE interface play a key role in the operation of FE/DE stack. These enormous trapped charges of  $10^{13}$ - $10^{14}$ /cm² at the FE/DE interface are supplied from the leakage current through the ultrathin DE layer. The proposed multi-probe measurement techniques provide a comprehensive understanding of FE/DE stack. The demonstrated leakage-assist polarization switching provides the new insights on the understanding of negative capacitance (NC) effect and ferroelectric device performance.

#### Introduction

Ferroelectric-gated field-effect transistor (FET) is widely studied as its application on non-volatile memory as ferroelectric FET (Fe-FET) and low power CMOS logic as negative capacitance FET (NC-FET) [1-4]. FE/DE stack is commonly applied in both Fe-FET and NC-FET. It is known that the FE/DE stack is fundamentally different from a FE capacitor and a DE capacitor in series due to the FE/DE interfacial coupling effect and charge accumulation at the FE/DE interface [5-13]. However, the physical mechanism of this coupling effect, especially the charge behaviors and interface trap properties, is still unclear.

In this work, interfacial charges in the FE/DE stack are characterized quantitatively. P-V and C-V techniques are firstly applied in the FE/DE stack to obtain the charge density during dynamic polarization switching. Furthermore, the conductance (G-V) method, which is widely used for the study of MOS interface [14], is for the first time formulated to measure the density of FE/DE interface traps. FE/DE interfacial charges considering both with and without polarization switching are clarified for FE devices towards logic and memory applications.

# **Device Fabrication**

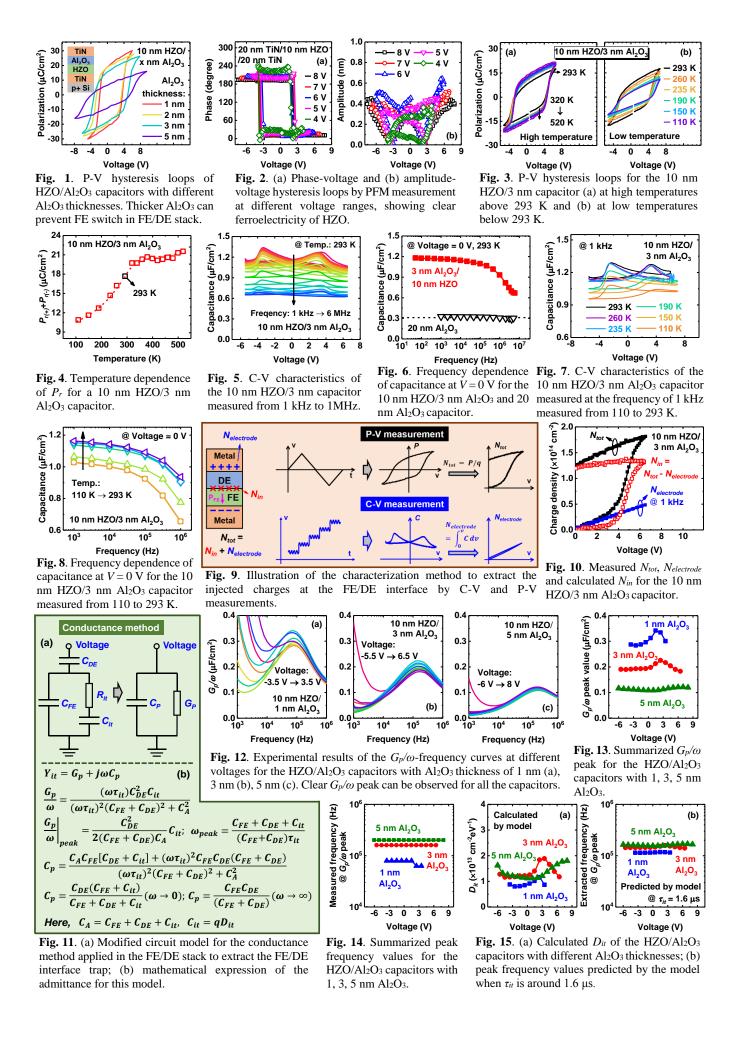

Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) is chosen as the FE layer and Al<sub>2</sub>O<sub>3</sub> is chosen as the DE layer to study the FE/DE interface properties. TiN, HZO and Al<sub>2</sub>O<sub>3</sub> were deposited by atomic layer deposition (ALD). TiN was deposited at 250 °C, using TDMAT and NH<sub>3</sub> as the Ti and N precursors. A 10 nm HZO (Hf:Zr=1:1) film was deposited at 200 °C, using TDMAHf, TDMAZr, and H<sub>2</sub>O as the Hf, Zr, and O precursors. The stacked Al<sub>2</sub>O<sub>3</sub> layer with four different thicknesses (1, 2, 3, 5 nm) was deposited at 200 °C, using TMA and H<sub>2</sub>O as Al and O precursors. Another TiN was deposited on the top of HZO/Al<sub>2</sub>O<sub>3</sub> stack. Finally, the samples were annealed at 500 °C in a N<sub>2</sub> ambient for 1 min by rapid thermal annealing. Fig. 1 shows the P-V properties of HZO/Al<sub>2</sub>O<sub>3</sub> capacitors with different Al<sub>2</sub>O<sub>3</sub> thicknesses. The significant decrease of remnant polarization (*P<sub>r</sub>*) in P-V hysteresis loops is observed with thicker DE layer, which is consistent with previously reported leakage-assist-switching mechanism [11]. Figs. 2(a) and 2(b) show phase-voltage and amplitude-voltage hysteresis loops by piezoresponse force microscopy (PFM) measurement, which further confirm the ferroelectricity of HZO.

## **Results and Discussion**

Figs. 3(a) and (b) show the temperature dependence of P-V properties for the 10 nm HZO/3 nm  $Al_2O_3$  capacitor at high and low temperatures. Fig. 4 summaries the  $P_r$  values at different temperatures. It is found that  $P_r$  is smaller at lower temperatures because of the reduction of leakage current and less charges provided for polarization switching. It indicates that this leakage-assist charge injection is a thermionic process instead of direct tunneling. To clarify this phenomenon, C-V measurements were performed at the 10 nm HZO/3 nm  $Al_2O_3$  capacitor with the frequencies ranging from 1 kHz up to 6 MHz (Fig. 5). Charge

injection behaviors are confirmed by large frequency dispersion. Capacitance of a 20 nm  $Al_2O_3$  capacitor was also measured as the control sample at different frequencies to exclude the influence of parasitic effect in the devices or the measurement setup (Fig. 6). Moreover, the C-V properties at low temperatures (Fig. 7) and at different frequencies (Fig. 8) were also measured. The smaller capacitance and larger frequency dispersion at lower temperatures further manifests the charge injection at the FE/DE interface.

To evaluate the density of injected charges, a simple approach with a combination of P-V and C-V measurements is proposed. As schematically shown in Fig. 9, the total polarization charge density ( $N_{tot}$ ) is provided by P-V loops, and the charge density on the electrodes ( $N_{electrode}$ ) is obtained by C-V curves. Then, injected charge density at the FE/DE interface ( $N_{in}$ ) can be calculated by subtracting  $N_{electrode}$  from  $N_{tot}$ . Fig. 10 exhibits surprisingly large  $N_{in}$  of  $\sim 10^{14}$  cm<sup>-2</sup> for the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> capacitor during dynamic polarization switching, which indicates that these injected charges are dominant for the polarization switching, similar to the phenomenon reported in the FE/DE stack [11] and also the Fe-FET [13]. It unveils that FE/DE interface is *not* fully investigated and understood. This *new* interface could play an important role in the device operations of Fe-FETs and NC-FETs.

In addition, G-V method is also for the first time applied in the metal/FE/DE/metal structure. As a small-signal measurement (30 mV), it is to characterize the interface traps at a steady polarization state. Fig. 11(a) shows the modified circuit model for this G-V method, which consists of the DE capacitance,  $C_{DE}$ , the FE capacitance,  $C_{FE}$ , the interface trap capacitance,  $C_{it}$ , and the loss of charge capture-emission by interface traps,  $R_{it}$ . Fig. 11(b) gives the mathematical expression of admittance for this circuit model, where the conductance,  $G_p$ , and capacitance,  $C_p$ , can be directly measured by LCR meter. It is found that,  $C_p$  is large at low frequency due to the immediate response of interface traps to the ac voltage, while  $C_p$  decreases at high frequency since the trap responses lag behind. This trend is consistent with the result observed in Fig. 6, suggesting the validation of the proposed model. By using this method, the  $G_p/\omega$ -frequency relationships are characterized for the HZO/Al<sub>2</sub>O<sub>3</sub> capacitors with different Al<sub>2</sub>O<sub>3</sub> thicknesses (Fig. 12). It is observed that the  $G_p/\omega$  peak value decreases and the peak frequency value increases with increasing the Al<sub>2</sub>O<sub>3</sub> thickness (Figs. 13 and 14). Fig. 15(a) shows the density of interface traps  $(D_{ii}) \sim 10^{13}/\text{cm}^2\text{eV}$  obtained from  $G_p/\omega$  peaks experimentally. Note that this is the interface trap responses to the small-signal measurement. It is fundamentally different from the charge density induced by ferroelectric polarization switching. Fig. 15(b) shows the extracted frequencies at  $G_p/\omega$  peak by the proposed model, with a time constant  $(\tau_{it})$  of ~1.6  $\mu$ s. The result agrees well with the measured data (Fig. 14), indicating the validity of conductance method applied in the FE/DE structure to characterize the FE/DE interface properties.

# Conclusion

The multi-probe C-V, P-V and G-V methods are applied to characterize the interfacial charge response at the FE/DE interface. The interfacial charge density is at  $\sim 10^{14}/\mathrm{cm^2}$  during dynamic polarization switching and  $D_{it} \sim 10^{13}/\mathrm{cm^2}\mathrm{eV}$  by small-signal response at a steady polarization state. The FE/DE interface is of importance to understand NC-FETs and Fe-FETs operations. The work is supported by SRC/DARPA JUMP ASCENT Center.

References: [1] J. Muller et al., Appl. Phys. Lett., 99, 112901, 2011. [2] K. Ni et al., IEEE TED, 65, 2461, 2018. [3] S. Salahuddin et al., Nano Lett., 8, 405, 2008. [4] W. Chung et al., IEDM, 365, 2017. [5] Y. J. Kim et al., J. Appl. Phys., 118, 224105, 2015. [6] A. Khan et al., IEEE TED, 63, 4416, 2016. [7] F. C. Sun et al., J. Mater. Sci., 51, 499–505, 2016. [8] Y. J. Kim et al., Nano Lett., 16, 4375, 2016. [9] M. Hoffmann et al., IEDM, 727, 2018. [10] M. A. Alam et al., Appl. Phys. Lett., 114, 090401, 2019. [11] M. Si et al., ACS Appl. Elec. Mat., 1, 745, 2019. [12] K. D. Kim et al., Adv. Funct. Mater., 29, 1808228, 2019. [13] K. Toprasertpong et al., IEDM, 570, 2019. [14] E. H. Nicollian et al., Bell Syst. Tech. J., 1055, 1967.