# RTN and Low Frequency Noise on Ultra-scaled Near-ballistic Ge Nanowire nMOSFETs

Wangran Wu<sup>1,2,3</sup>, Heng Wu<sup>1</sup>, Mengwei Si<sup>1</sup>, Nathan Conrad<sup>1</sup>, Yi Zhao<sup>2,3</sup> and Peide D. Ye<sup>1\*</sup>

<sup>1</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907, U.S.A.

<sup>2</sup>School of Electronic Science and Engineering, Nanjing University, Nanjing, 210093, China

<sup>3</sup>State Key Laboratory of Silicon Materials, Zhejiang University, Hangzhou, 310027, China

\*Email: yep@purdue.edu

#### **Abstract**

In this work, we present the first observation of random telegraph noise (RTN) in ultra-scaled Ge nanowire (NW) nMOSFETs. The impacts of NW geometry, channel length, EOT, and channel doping on low frequency noise are studied comprehensively. It is confirmed that the low frequency noise with 1/f characteristics is attributed to the mobility fluctuation in ultra-scaled Ge NW nMOSFETs. The low frequency noise decreases when the channel length scales down from 80 nm to 40 nm because of the near-ballistic transport of electrons.

#### Introduction

Ge channel is one of the promising candidates for future ultimate CMOS applications because Ge has high and balanced electron and hole mobility, good compatibility with Si large-scale-integration technologies and great potential for voltage scaling [1-2]. Ge CMOS has been intensively studied in the past decade and highly scaled Ge NW CMOS has been demonstrated to offer excellent performance [3-5]. However, advanced high-k/Ge gate stacks with scaled EOT and superior MOS interfaces are still needed to develop Ge CMOS manufacturing technology with high reliability [6]. The conventional C-V method and charge pumping method cannot be applied to ultrasmall devices without a body contact. It is increasingly hard to directly measure the interface and oxide property when the devices are aggressively scaled down to sub-100 nm. Therefore, low frequency noise and RTN can be used as alternate probes for device characterization and process optimization since noise measurement is not limited by the small gate capacitance [7-9]. In the meanwhile, low frequency noise and RTN have serious impacts in scaled nonvolatile memories and logic circuits [10-11]. Several groups have reported low frequency noise study of long channel Ge MOSFETs [12-13]. There is still no study on low frequency noise and RTN of highly scaled Ge MOSFETs with sub-100 nm gate length.

In this paper, we: 1) report the first observation of RTN in ultrascaled Ge NW nMOSFETs and extract the basic parameters of the traps; 2) examine the origin of the 1/f low frequency noise; 3) systematically study the properties of low frequency noise on Ge NW nMOSFETs with various NW geometries (NW width,  $W_{\rm NW}$ , NW height,  $H_{\rm NW}$ ), channel length ( $L_{\rm ch}$ ), EOT and channel doping.

## **Experiments**

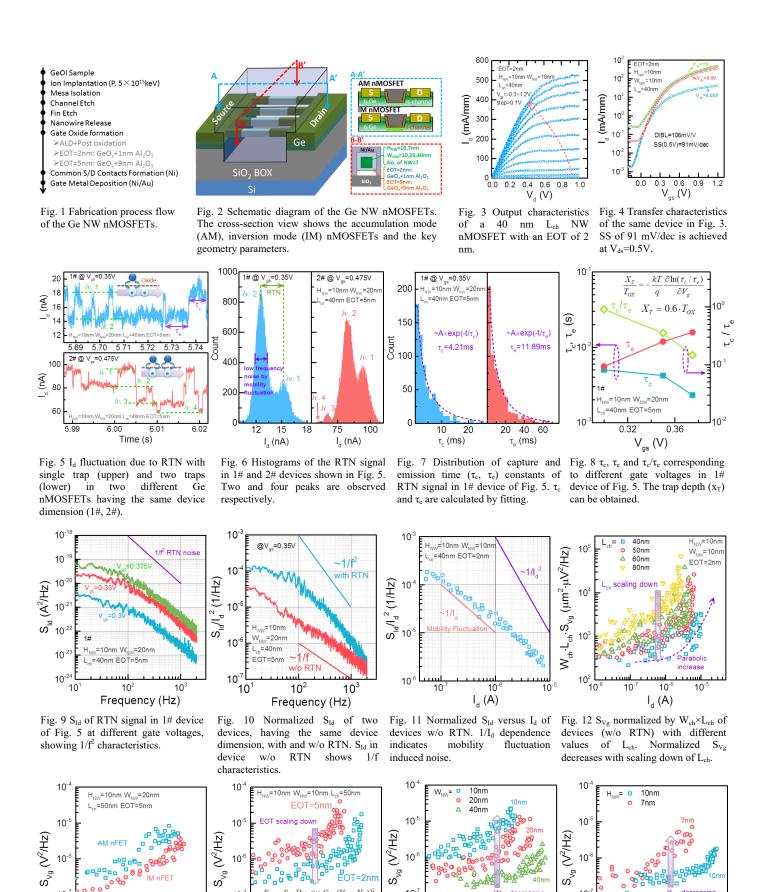

The fabrication process is shown in Fig. 1, which is the same as reported in Ref. [5]. Fig. 2 illustrates the schematic image of the Ge NW nMOSFETs. The cross-section view shows the accumulation mode (AM), inversion mode (IM) nMOSFETs and the key geometry parameters of devices. Ge NW nMOSFETs with  $W_{\rm NW}$  from 10 nm to 40 nm,  $H_{\rm NW}$  of 7 nm and 10 nm,  $L_{\rm ch}$  from 40 nm to 80 nm and EOT of 2 nm and 5 nm are used for RTN and low frequency noise characteristics. The channel width is calculated from  $W_{\rm ch}=(2\cdot H_{\rm NW}+W_{\rm NW})\times (\text{number of wires})$  and each device has 7 nanowires. AM NW nMOSFETs are measured unless otherwise specified. Keysight B1500A with B1530A Waveform Generator/Fast Measurement Unit is applied for characterization. All the measurements were performed at room temperature at a drain voltage  $(V_{\rm ds})$  of 50 mV.

### **Results and Discussion**

A. RTN characteristics: Figs. 3-4 show the good output and transfer characteristics of a Ge NW nMOSFET with  $L_{ch}$  of 40 nm and EOT of 2 nm. Typical RTN signal of drain current ( $I_d$ ) with signal trap and two traps are illustrated in Fig. 5. Two and four distinct current switching levels are observed in the two devices with the same device dimension. The trap number n can be estimated from current fluctuation levels N via  $2^{n-1} < N \le 2^n$ . The corresponding histograms of  $I_d$  with two and four peaks are shown in Fig. 6. The histograms show the superposition of RTN signal and mobility fluctuation (1/f) noise. Average time constants in single trap RTN,

such as capture time constant  $(\tau_c)$  and emission time constant  $(\tau_e)$ , are extracted by exponential fitting to time constants distributions (Fig. 7).  $\tau_c$  and  $\tau_e$  may change with gate voltage  $(V_{gs})$  because of the move of Fermi level. Clear RTN signals were observed when  $V_{gs}$  was near threshold voltage  $(V_{th})$ . The relation between  $\tau_c$ ,  $\tau_e$ ,  $\tau_c/\tau_e$  and  $V_{gs}$  is shown in Fig. 8. The negative correlation between  $\tau_c/\tau_e$  and  $V_{gs}$  indicates that the electrons' trapping and de-trapping occur between channel and gate oxide [9]. The depth of this trap from the interface  $(x_T)$  in the gate oxide can be calculated according to the formula in Fig. 8. For the trap in 1# device of Fig. 5,  $x_T$  equals to  $0.6T_{\rm OX}$  (oxide thickness), indicating that it is a deep trap.

**<u>B. Low frequency noise:</u>** Fig. 9 shows the power spectrum density (PSD) of I<sub>d</sub> (S<sub>Id</sub>) in 1# device of Fig. 5 under different gate voltages. Typical Lorentzian spectrum with 1/f<sup>2</sup> characteristics is observed. The low frequency noise increases with higher V<sub>gs</sub>. The normalized  $S_{Id}$  ( $S_{Id}/I_d^2$ ) between two devices, sharing the same device dimension, with and without RTN signal is compared in Fig. 10. The noise spectrum of device without RTN shows 1/f characteristics. The low frequency noise results ( $S_{\text{Id}},\ S_{\text{Vg}})$  in Figs. 11-16 are obtained in devices without RTN at a frequency of 10 Hz and each group of the data contains experimental results from several devices sharing the same device dimension. Fig. 11 shows the normalized  $S_{Id}$  ( $S_{Id}/I_d^2$ ) as a function of I<sub>d</sub>. The clear 1/I<sub>d</sub> dependence agrees well with the mobility fluctuation model [14]. Fig. 12 presents the input gate noise  $(S_{Vg}=S_{Id}/g_m^2)$  normalized by channel area  $(W_{ch}\cdot L_{ch}\cdot S_{Vg})$  versus  $I_d$ . The normalized  $S_{\mathrm{Vg}}$  decreases when the  $L_{ch}$  scales down, while the classical theory indicates  $W_{ch} \cdot L_{ch} \cdot S_{Vg}$  shall be independent of channel area [14]. The anomalous scaling trend of low frequency noise can be attributed to the near-ballistic transport of electrons in the channel. Because of the electron's long mean free path in Ge, electrons encounter less scattering at smaller Lch. Therefore, the scattering induced mobility fluctuation decreases at small Lch, thus the normalized  $S_{\mathrm{Vg}}$  reduces. Similar results were also observed in highly scaled InGaAs MOSFETs as reported in Ref. [15]. Also, the parabolic increase of S<sub>Vg</sub> confirms again the low frequency noise is attributed to the mobility fluctuation other than the carrier number fluctuation [16]. Since scattering is an important source of low frequency noise,  $S_{Vg}$  is smaller in IM NW MOSFETs because the relative lower channel doping would induce less Coulomb scattering (Fig. 13). S<sub>Vg</sub> decreases in device with smaller EOT because of the enhancement of gate control (Fig. 14). The change in NW geometries affects the low frequency noise due to the change of channel area. Since low frequency noise is inversely proportional to the channel area,  $S_{Vg}$  increases with the decrease in  $W_{NW}$  and  $H_{NW}$ (Figs. 15-16). In the perspective of device performance, the increase of H<sub>NW</sub> promises the enhancement of on-state performance, i.e., I<sub>d</sub> and g<sub>m</sub> per pitch area, and the suppression of low frequency noise.

### Conclusion

We report the first observation of RTN in Ge NW nMOSFETs. The mobility fluctuation is confirmed to be the source of low frequency noise in ultra-scaled Ge NW nMOSFETs other than the carrier number fluctuation. Because of the long mean free path of electrons in Ge, the low frequency noise is suppressed at shorter channel due to the near-ballistic transport at sub-100 nm region. Therefore, ultra-scaled Ge NW MOSFETs with low channel doping, small EOT and high  $H_{\rm NW}$  are promising in the performance enhancement as well as the suppression of low frequency noise.

## Reference

[1] A. Toriumi, et al., *IEDM*, p. 28.4.1, 2011. [2] D. Kuzum, et al., *TED*, **58**, 8, 2011. [3] C. Chung, et al., *IEDM*, p.16.4.1, 2012. [4] R. Pillarisetty, *Nature*, p. 324, 2011. [5] H. Wu, et al., *IEDM*, p. 16-19, 2015. [6] R. Zhang, et al., *TED*, **60**, 3, 2013. [7] T. Grasser, et al., *IEDM*, p.681, 2009. [8] E.R. Hsieh, et al., *VLSI*, p. 1-2. 2014. [9] T. Nagumo, et al., *IEDM*, p. 28.3.1, 2010. [10] M.L. Fan, *TED*, **59**, 8, 2012. [11] J. Zou, et al. *VLSI*, P. T186, 2013. [12] E. Simoen, et al., *TED*, **58**, 9, 2011. [13] W. Fang, et al., *TED*, **62**, 7, 2015. [14] G. Ghibaudo, et al., *Microelectron. Rel.*, **42**, 4, 2002. [15] M. Si, et al., *TED*, **62**, 11, 2015. [16] J. Lee, et al. *FDL*, **24**, 1, 2003.

Fig. 13  $S_{Vg}$  versus  $I_d$  in AM and IM nMOSFETs. Svg is smaller in IM nMOSFETs because of the less Coulomb scattering in the channel.

10

$I_d(A)$

10

10

Fig. 14 S<sub>Vg</sub> versus I<sub>d</sub> in devices with different EOT.  $S_{\mathrm{Vg}}$  decreases with the scaling down of EOT because of the enhanced gate control.

$\lambda kTq^2N$

fWLC

10

Fig. 15 S<sub>Vg</sub> versus I<sub>d</sub> in devices with different  $\tilde{W}_{NW}$ .  $S_{Vg}$  increases with the scaling down of W<sub>NW</sub> because of the decrease of the gate areas.

=10nm L

10

=60nm EOT=5nm

10

10-

$I_d(A)$

10

10-

10

rrind

10-5

10<sup>-6</sup>

$I_d(A)$

Fig. 16 S<sub>Vg</sub> versus I<sub>d</sub> in devices with different  $H_{NW}$ .  $S_{Vg}$  increases with the decrease in H<sub>NW</sub> because of the decrease of the gate areas.

10

10

$I_d(A)$

10

10

10